In the fast-paced world of Electronic Design Automation (EDA), the complexity of chip designs is continuously rising. With the burgeoning of systems such as 5G communication devices and Advanced Driver-Assistance Systems (ADAS) teeming with thousands of components, the demand for robust and efficient prototyping platforms… Read More

Tag: pcie

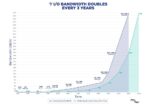

AI System Connectivity for UCIe and Chiplet Interfaces Demand Escalating Bandwidth Needs

Artificial Intelligence (AI) continues to revolutionize industries, from healthcare and finance to automotive and manufacturing. AI applications, such as machine learning, deep learning, and neural networks, rely on vast amounts of data for training, inference, and decision-making processes. As AI algorithms become … Read More

Webinar: Samtec and Achronix Expand AI in the Data Center

The performance demands of data centers continue to grow, driven to large degree by the ubiquitous use of complex AI algorithms. On April 25, Embedded Computing Design held an informative webinar on this topic. Two experts looked at the problem from the standpoint of processor architecture and communication strategies, which… Read More

Alphawave Semi Bridges from Theory to Reality in Chiplet-Based AI

GenAI, the most talked-about manifestation of AI these days, imposes two tough constraints on a hardware platform. First, it demands massive memory to serve large language model with billions of parameters. Feasible in principle for a processor plus big DRAM off-chip and perhaps for some inference applications but too slow … Read More

Synopsys 224G SerDes IP’s Extensive Ecosystem Interoperability

Hyperscale data centers are evolving rapidly to meet the demands of high-bandwidth, low-latency applications, ranging from AI and high-performance computing (HPC) to telecommunications and 4K video streaming. The increasing need for faster data transfer rates has prompted a scaling of Ethernet from 51Tb/s to 100Tb/s. Numerous… Read More

CEO Interview: Sanjeev Kumar – Co-Founder & Mentor of Logic Fruit Technologies

Sanjeev is a renowned technopreneur in the semiconductor industry. With more than 20+ years of experience, he is known for his enormous resilience and deep tech knowledge that sets him apart from others in the industry.

Sanjeev started his career as a hardware designer and then forayed into the FPGA domain due to his love for configurable… Read More

WEBINAR: Why Rigorous Testing is So Important for PCI Express 6.0

In the age of rapid technological innovation, hyperscale datacenters are evolving at a breakneck pace. With the continued advancements in CPUs, GPUs, accelerators, and switches, faster data transfers are now paramount. At the forefront of this advancement is PCI Express (PCIe®), which has become the de-facto standard of interconnect… Read More

PCI-SIG DevCon and Where Samtec Fits

PCIe (peripheral component interconnect express) is an interface standard for connecting high-speed components contained in PCs, MACs and other types of processors. Think graphics, storage arrays, Wi-Fi and the like. This communication standard has become incredibly popular. The first version of the standard was released… Read More

S2C Helps Client to Achieve High-Performance Secure GPU Chip Verification

S2C, a leading provider of FPGA-based prototyping solutions, has helped a client achieve high-performance secure GPU chip verification. With the help of S2C’s Prodigy prototyping solution, the client was able to start software development and hardware-software co-design early, leading to accelerated time-to-market… Read More