A semiconductor SoC design can have multiple components at different levels of abstractions from different sources and in different languages. While designing an SoC, IPs at different levels have to be integrated without losing the overall design goals. Of course, quality of an IP inside and outside of an SoC must be tested thoroughly.… Read More

Tag: mixed signal

Xilinx’s Mixed Signal FPGA

Something in all the Xilinx chatter of UltraScale 20nm, 16nm, having massive amounts of Gigabit transceivers, DSP blocks, RAM, HLS, Rapid Design Closure gets lost… and that is Xilinx’s ability for Mixed Signals. I do not mean when you are talking with the wife (Remember Listen!), but a wonderful block that lives within… Read More

Cadence’s Mixed-Signal Technology Summit

On October 10, I attended another Cadence Summit, this one titled the Cadence Mixed-Signal Technology Summit. Recently, I had written about the Cadence Silicon Verification Summit. The verification event was the first of its kind, and I thought it had terrific content. Being more of a digital guy myself, I was unaware that Cadence… Read More

Mixed Signal SOC verification Webinar

When looking at the time to design and verify an SoC we’ve known for many years now that the verification effort requires more time than the design process. So anything that will shorten the verification effort will have the biggest impact on keeping your project on schedule.

A second trend is the amount of Analog content in… Read More

When the lines on the roadmap get closer together

Tech aficionados love roadmaps. The confidence a roadmap instills – whether using tangible evidence or just a good story – can be priceless. Decisions on “the next big thing”, sometimes years and a lot of uncertain advancements away, hinge on the ability of a technology marketing team to define and communicate a roadmap.

Any roadmap… Read More

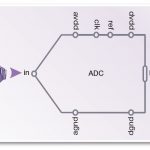

Integrating your SoC into the analog world

Our world is decidedly analog, made up of stimuli for our five basic senses of sight, touch, hearing, taste, and smell, and more advanced senses like balance and acceleration. To be effective on the Internet of Things, digital devices must integrate with the analog world, interfacing with sensors and control elements.… Read More

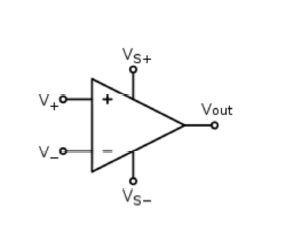

How accurate are AMS Behavioral Models?

You often hear the mantra that Analog Mixed-Signal (AMS) behavioral models are inaccurate. It is repeated so often that it starts to morph into “AMS models are inherently inaccurate”. This is not true.

Source: Wikipedia

… Read More

An AMS Reference Flow for Power Management Designs

At DAC in June I visited and blogged about 30+ EDA and Semi IP companies, however I didn’t have time to watch the TowerJazz presentation in the Cadence Theater entitled: AMS Flow for Power Management Designs. Today I watched the 26 minute video and have summarized what I learned in this blog post.… Read More

Hybrids on BeO then, 3D-IC in silicon now

Once upon a time (since every good story begins that way), I worked on 10kg, 70 mm diameter things that leapt out of tubes and chased after airplanes and helicopters. The electronics for these things were fairly marvelous, in the days when surface mount technology was in its infancy and having reliability problems in some situations.… Read More

Cadence Mixed Signal Technology Summit

Yesterday I attended some of the Cadence mixed-signal technology summit. The day ended with a panel session on Are We Closing the Gap Yet in Mixed-signal Design? Richard Goering moderated. The panelists were all mixed signal experts:

- Nayaz Khan of Maxim

- Nishant Shah of Broadcom

- Shiv Sikand of IC Manage

- Bill Meier of Texas Instruments