In the early days an IC had a single clock and a single reset signal, making it a simple matter to reset the chip into a known, stable state, so there was little need for detailed analysis. For modern designs there can be dozens to hundreds of clocks, creating separate domains and some use of asynchronous resets, so the challenge of ensuring… Read More

Tag: metastability

How to Find and Fix Soft Reset Metastability

Most of us are familiar with the metastability problems that can be caused by clock domain crossings (CDC). Early static analysis techniques can flag these kinds of issues to ensure there are no surprises later. I spent quite a bit of time at Atrenta, the SpyGlass company, so I am very familiar with these challenges. Due to the demands… Read More

Handling metastability during Clock Domain Crossing (CDC)

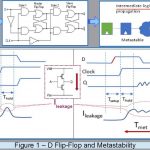

SoC designs frequently have lots of different clock domains to help manage power more efficiently, however one side effect is that when the clock domains meet, i.e., in a Clock Domain Crossing (CDC), there’s the possibility of setup and hold time violations that can cause a flip-flop to become metastable. Synchronizer … Read More

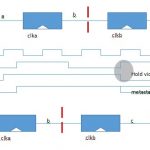

Clock Domain Crossing in FPGA

Clock Domain Crossing (CDC) is a common occurrence in a multiple clock design. In the FPGA space, the number of interacting asynchronous clock domains has increased dramatically. It is normal to have not hundreds, but over a thousand clock domains interactions. Let’s assess why CDC is a lingering issue, what its impact and the … Read More

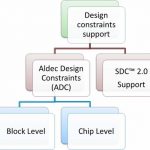

Aldec updates two EDA product lines

Continuous, incremental improvement based on customer feedback and insight from researchers is a pillar of the Aldec EDA strategy. Within the last two weeks, two of the Aldec product lines – Riviera-PRO, and ALINT-PRO-CDC – have seen new version releases. Here’s a quick look at some of the highlights of both.

Riviera-PRO 2015.06… Read More

Synchronizer Optimization 101

A webinar presented Last week introduced two free aids to evaluating synchronizer Mean Time Between Failures (MTBF). The first, MetaACE LTD, is used to characterize the intrinsic parameters needed to calculate MTBF (tau and Tw). This limited version of MetaACE supports up to 250 circuit nodes, which is enough for a typical C-only-extracted… Read More

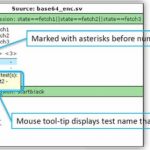

Writing the unwritten rules with ALINT-PRO-CDC

EDA verification tools generally do a great job of analyzing the written rules in digital design. Clock domain crossings (CDCs) are more like those unwritten rules in baseball; whether or not you have a problem remains indefinite until later, when retaliation can come swiftly out of nowhere.

Rarely as overt or dramatic as a bench-clearing… Read More

A Public Synchronizer

You might ask yourself “Why would anyone want to have a public synchronizer available to download?” Usually designers just grab a flip-flop from his or her company’s or a standard cell vendor’s library. However, are these handy solutions the best course of action today? Current SoC designs have numerous clock domains providing… Read More

Measuring Metastability

Measuring metastability is just 50 years old this year. In 1965 my colleague Tom Chaney took a sampling ‘scope picture of an ECL flip-flop going metastable. S. Lubkin had made mention of the phenomenon over a decade before that, but at that time most engineers were unaware of the phenomenon or did not believe it actually existed. … Read More

Dominating FPGA clock domains and CDCs

Multiple clock domains in FPGAs have simplified some aspects of designs, allowing effective partitioning of logic. As FPGA architectures get more flexible in how clock domains, regions, or networks are available, the probability of signals crossing clock domains has gone way up.… Read More