The ECU. That was the service department prognosis on the root cause of thealways-on air bag safety light on my immaculate car. Ten years ago the cost for its replacement with after market part was at par with getting a new iPhone 8. Today, we could get four units for the same price and according to data from several research companies,… Read More

Tag: mentor

Affordable EDA Tools for IoT Designs, Guess which Vendor

I just had to drive my car 7 miles from Tualatin, Oregon to visit with an EDA veteran who has played a lot of diverse roles in his career, including: IC Mask Designer, Layout Manager, Account Manager, Business Development, Director, Foundry Relations Director. His name is John Stabenow, with Mentor, a Siemens Business, and we met… Read More

The Pain of Test Pattern Bring-up for First Silicon Debug

In the semiconductor world we have divided our engineering talent up into many adjacent disciplines and each comes with their own job titles: Design engineers, Verification engineers, DFT engineers, Test engineers. When first silicon becomes available then everyone on the team, and especially management all have a few big … Read More

Harnessing Clock and Power

Switching translates to power. Similar to the recent slow down experienced by Moore’s Law, the constant power density (power demand per unit chip area) prescribed by Dennard scaling was no longer affordable across the technological scaling. While the contribution of leakage power component in advanced process nodes was getting… Read More

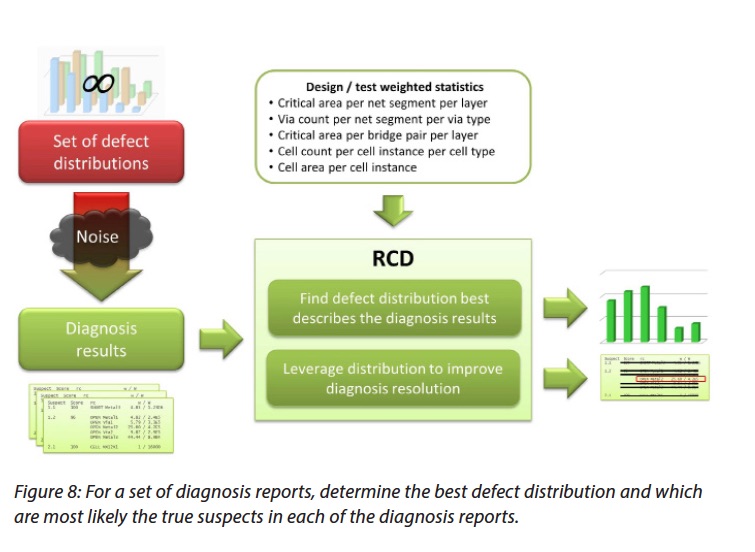

Machine Learning Meets Scan Diagnosis for Improved Yield Analysis

Naturally, chips that fail test are a curse, however with the advent of Scan Logic Diagnosis these failures can become a blessing in disguise. Through this technique information gleaned from multiple tester runs can help pin down the locations of defects. Initially tools that did Scan Logic Diagnosis relied on the netlist to filter… Read More

Mentor Calibre Panel

Getting your tape-out done on time is hard, but can it be made easier? That was the main topic of Mentor’s Calibre Panel held at DAC 2018, attended by a few key players in IC design ecosystem: Bob Stear, VP of Marketing at Samsung represented the foundry side; from the IP side, Prasad Subramaniam, VP of eSilicon for R&D and Technology;… Read More

Mentor at the 55th Design Automation Conference

It’s hard to believe that this is the 55th DAC and even harder to believe that this will be my 35th. So much has changed in 35 years, with DAC back in San Francisco I expect a VERY big crowd and even bigger announcements, absolutely.

Not only is this an epic time for semiconductors, I would say that EDA is exciting again and the Mentor… Read More

Achieving Clean Design Early with Calibre-RTD

Functional and physical verification are easily the two long poles in most IC product developments. During a design implementation cycle, design teams tend to push physical verification (PV) step towards the end as it is a time consuming process and requires significant manual interventions.

PV Challenges

In the traditional… Read More

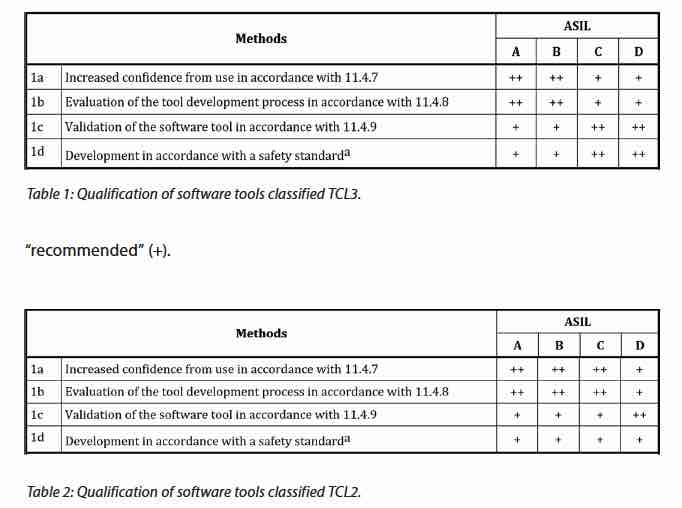

ISO 26262: Automotive electronics safety gets an update in 2018

In the field of automotive electronics, the year 2011 was a long time ago. So, it is about time that the initial ISO 26262 specification that was adopted back then gets an update. The latest version will be known as ISO26262:2018 and will expand the scope of the original to cover more types of vehicles. It will add an entire section on… Read More

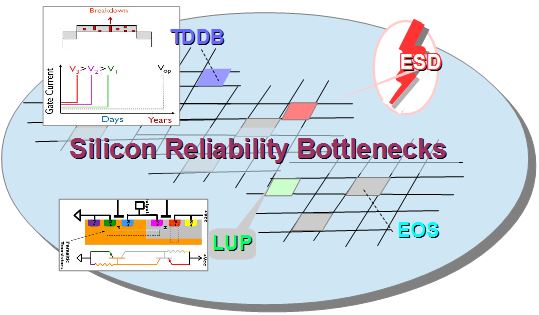

Electrical Reliability Verification – Now At FullChip

Advanced process technology offers both device and interconnect scaling for increased design density and higher performance while invoking also significant implementation complexities. Aside from the performance, power and area (PPA) aspects, designer is getting entrenched with the need of tackling more reliability … Read More