Innovations in packaging have played an important role in improving system performance and area utilization. Advances like 2.5D interposers and fan-out wafer-level packaging (FOWLP) have allowed mixed dies to be used in a single package and have dramatically reduced the number of connections that need to go all the way to the… Read More

Tag: mentor

ITC shines light on new Mentor Test announcements

The 50th International Test Conference was just held in Washington DC, where papers, sessions, workshops and announcements addressing the increasing complexity and expanding use of semiconductors showed that innovations in test are crucial to design and product success. Test methodologies and even the scope of test have … Read More

Mentor’s Questa verification tools now run on 64-bit ARM based servers

The server market has been undergoing changes in the last few years. The traditional go-to for server processors had been x86 based chips from Intel or AMD. However, if you go on Amazon AWS looking for EC2 instances, you will see the “A1” instance type, which is an ARM based instance. This is not what you might think at first. The A1 instance… Read More

Can a hierarchical Test flow be used on a flat design?

It is pretty common for physical layout to work from a flattened hierarchy for blocks or even full chips, even though the front-end design starts with a hierarchical representation. This was not always the case. Way back when, the physical layout matched the logical hierarchy during the design process. Of course, this led to all… Read More

Accelerate Your Early Design Recon

A product launch nowadays demands shorter runway. SoC designers challenges are not so much in facing the unavailability of proven design capture methodologies or IP’s that could satisfy their product requirements, but more so in orchestrating the integration of all those components to deliver the targeted functionalities… Read More

Automotive Market Pushing Test Tool Capabilities

It’s easy to imagine that the main impetus for automotive electronics safety standards like ISO 26262 is the emergence of autonomous driving technology. However, even cars that do not offer this capability rely heavily on electronics for many critical systems. These include engine control, braking, crash sensors, and stability… Read More

An Important Next Step for Portable Stimulus Adoption

Portable stimulus has been a hot topic for a couple of years in the EDA and semiconductor industries. Many observers see this approach as the next major advance in verification beyond the Universal Verification Methodology (UVM), and the next step higher in abstraction for specifying verification intent. The basic idea is to … Read More

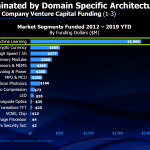

The Implications of the Rise of AI/ML in the Cloud

Recently, Daniel Nenni blogged on the presentation Wally Rhines gave at #56th DAC. Daniel provided a great summary, but I want to dive into a portion of the presentation in more detail. I love Wally’s presentations, but sometimes you cannot absorb the wealth of information he provides when you initially see it. It’s… Read More

Siemens Shows SOC Simulation Solution for Self-Driving Vehicles

Ever since the early days of computing there has always been a large distinction between ‘regular’ computing and real time computing – where special care had to be made to deal with unordered and asynchronous events. Back then a system typically consisted of a handful of sensors and perhaps some electromechanical devices.… Read More

Deep Learning, Reshaping the Industry or Holding to the Status Quo

AI, Machine Learning, Deep Learning and neural networks are all hot industry topics in 2019, but you probably want to know if these concepts are changing how we actually design or verify an SoC. To answer that question what better place to get an answer than from a panel of industry experts who recently gathered at DVcon with moderator… Read More