You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

DFM closure is a growing issue these days even at the 45nm node, and IC designers at ST-Ericsson have learned that transitioning from dummy fill to SmartFill has saved them time and improved their DFM score.

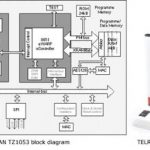

The SOC

ST-Ericsson designed an SOC for mobile platforms called the U8500 and their foundry choice was a 45nm node at STMicroelectronics… Read More

I read about how Toumaz used the Analog Fast SPICE (AFS) tool from BDA and it sounded interesting so I setup a Skype call with Alan Wong in the UK last month to find out how they design their ultra low-power IC chips.

Interview

Q: Tell me about your IC design background.

A: I’ve been at Toumaz almost 8 years now and before that at Sony… Read More

Intro

Mentor, Cadence and Synopsys all offer Verilog simulators, however when was the last time that you benchmarked your simulator against a tool from a smaller company?

I just heard from an RTL designer (who wants to remain anonymous) about his experience comparing a Verilog simulator called CVC from Tachyon against ModelSim… Read More

There are various rumors around about Cadence starting to close up stuff that has been open for a long time. Way back in the midst of time, as part of the acquisition of CCT, the Federal Trade Commission forced Cadence to open up LEF/DEF and allow interoperability of Cadence tools (actually only place and route) I believe for 10 years.… Read More

The CEO panel at the 2nd GTC wasn’t especially enlightening. The theme was that going forward will require cooperation for success and everyone was really ready to cooperate.

The most interesting concept was Aart talking about moving from what he called “scale complexity” aka Moore’s law to what he … Read More

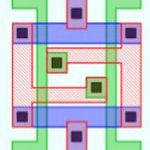

I met with Jeff Wilson, Product Marketing Manager at Mentor in the Calibre product group to learn more about Smart Fill versus Dummy Fill for DFM flows. Jeff works in the Wilsonville, Oregon office and we first meet at Silicon Compilers back in the 1990’s.

Dummy Fill

This diagram shows an IC layout layer on the left as originally… Read More

Can Your Router Handle 28 nm?by Beth Martin on 06-20-2011 at 7:11 pmCategories: EDA, Siemens EDA

With the adoption of the 32/28 nm process node, some significant new challenges in digital routing arise—including complex design rule checking (DRC) and design for manufacturing (DFM) rules, increasing rule counts, very large (1 billion transistor) designs. To meet quality, time-to-market, and cost targets, design teams… Read More

Introduction

IC designs go through a layout process and then a verification of that layout to determine if the layout layer width and spacing rules conform to a set of manufacturing design rules. Adhering to the layout rules will ensure that your chip has acceptable yields.

At the 28nm node a typical DRC (Design Rule Check) deck will… Read More

I was at Wally’s u2u (Mentor user group) keynote yesterday. The other keynote was by Ivo Bolsens of Xilinx and is here. He started off by looking at how the semiconductor industry has recovered and silicon area shipments are now back on trend after a pronounced drop in 2009 and revenue has followed. Finally the semiconductor… Read More