In part I of this series, we looked at the history of lithography process models, starting in 1976. Some technologies born in that era, like the Concorde and the space shuttle, came to the end of their roads. Others did indeed grow and develop, such as the technologies for mobile computing and home entertainment. And lithography … Read More

Tag: mentor

Getting Real Time Calibre DRC Results

Last week I met with Joseph Davis, Ph.D. at Mentor Graphics in Wilsonville, Oregon to learn about a new product designed for full-custom IC layout designers to improve productivity.

The traditional flow for full-custom IC layout designers has been nearly unchanged for decades:

- Read a schematic or use Schematic Driven Layout

Wally Rhines DvCon 2011 Ketnote: From Volume to Velocity

Abstract:

There has been a remarkable acceleration in the adoption of advanced verification methodologies, languages and new standards. This is true across all types of IC design and geographic regions. Designers and verification engineers are surprisingly open to new approaches to keep pace with the relentless rise in design… Read More

Mentor Graphics Should Be Acquired or Sold: Carl Icahn COUNTERPOINT

Daniel,

On Jan 20th, you criticized that the EDA models are all broken and need to change. Ridiculing Synpsys, Cadence, Mentor and Magma for not agreeing to ‘pay for success’ type of model (some form of royalties).

On Feb 14th, you state thatIcahn doesn’t understand EDA and should stay out. Maybe he is seeing … Read More

Mentor Graphics to Participate in SemiWiki.com Social Media Platform

San Jose, Calif., [DATE], 2011 – SemiWiki.com today announced that Mentor Graphics, a world leader in electronic hardware and software design solutions, will participate in the SemiWiki.com global social media platform aimed at facilitating mass communication for electronic design professionals through Web 2.0 technologies.… Read More

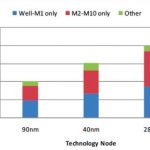

EDA and Wall Street

Good news in a way: Merrill Lynch (or Bank of America Merrill Lynch as I suppose we have to get used to calling them) have re-started coverage of EDA with a 20 page report on the industry, much of which is spent on explaining how the industry segments out and who is strong in which segments, stuff that most people reading this site already… Read More

DRC+, DFM, CMP, Variablility

When I worked at Intel as a circuit design engineer I could talk directly with the technology development engineers to understand how to really push my DRAM designs and get the smallest possible memory cell layout that would still yield well, provide fast access time, and long refresh cycles.

(United States Patent 6661699. Inventor:… Read More

Getting to the 32nm/28nm Common Platform node with Mentor IC Tools

Last week I talked with two experts at Mentor about the challenges of getting IC designs into the 32nm/28nm node on the Common Platform (IBM, GLOBALFOUNDRIES and Samsung). Global Foundries issued a press release talking about how the four major EDA companies have worked together to qualify EDA tools for this node.

Sudhakar Jilla,… Read More

The Future of Semiconductor Design!

Is EDA still an appropriate term for what we do? What applications will drive future semiconductor design innovation? Will further consolidation be required for EDA to thrive again? They are all good questions, questions that will hopefully be properly addressed at the EDAC CEO Forecast and Industry Vision event next week but… Read More

Mentor – Cadence Merger and the Federal Trade Commission

More consolidation is coming to EDA and so is the Federal Trade Commission. Corporate raider Carl Ichan owns 15% of Mentor Graphics and now owns 1% of Cadence. Ichan buddy multi billionaire George Soros, a long time CDNS investor, just purchased more than 76 million convertible notes of MENT.You do the math…

Unfortunately the FTC… Read More