Last month in DAC I could see some of the top innovations in the EDA world. EDA is a key enabler for advances in semiconductor designs. Among a number of innovations worth mentioning (about which I blogged just after DAC), the integration of Mentor’s Veloce with ANSYS’ PowerArtist for power analysis of live applications caught my… Read More

Tag: mentor

Power Management Gets Tricky in IP Driven World

Today, an SoC can have multiple instances of an IP and also instances of many different IPs from different vendors. Every instance of an IP can work in a separate mode and requires a dedicated power arrangement which may only be formalized at the implementation stage. The power intent, if specified earlier, will need to be re-generated… Read More

What’s New in Functional Verification Debug

We often think of EDA vendors competing with each other and using proprietary data formats to make it difficult for users to mix and match tools, or even create efficient flows of tools. At the recent DAC event in San Francisco I was pleasantly surprised to hear that two EDA vendors decided to cooperate instead of create incompatible… Read More

Predicting Lifetime of Analog ICs

With the increase of transistors per unit area, high density interconnects and manufacturing variability at lower nodes, the electronic devices have become more vulnerable to failures. The devices that operate under extreme conditions such as automotive devices that operate at high temperatures need to be robust enough to… Read More

Can FD-SOI Change the Rule of Game?

It appears so. Why there is so much rush towards FD-SOI in recent days? Before talking about the game, let me reflect a bit on the FD-SOI technology first. The FD-SOI at 28nm claims to be the most power-efficient and lesser cost technology compared to any other technology available at that node. There are many other advantages from… Read More

Eyes Meet Innovations at DAC

It gives me a very nice, somewhat nostalgic, feeling after attending the 52[SUP]nd[/SUP] DAC. There was a period during my final academic year in 1990 and my first job when I used to search through good technical papers in DAC proceedings and try implementing those concepts in my project work. In general, representation from ‘R&D… Read More

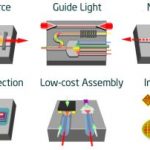

Why silicon photonics and 2.5D design go together

Silicon photonics is one of the upstart “More than Moore” technologies designed to enable the next generation of high-performance devices. Photonic design is the art of moving and transforming signals in the form of photons, allowing the message to literally travel at the speed of light, and bringing the promise of significant… Read More

Experts Talk at Mentor Booth

It’s less than four weeks to go at DAC 2015 and the program is final now. So I started investigating new technologies, trends, methodologies, and tools that will be unveiled and discussed in this DAC. In the hindsight of the semiconductor industry over the last year, I see 14nm technologies in the realization stage and 10nm beckoning… Read More

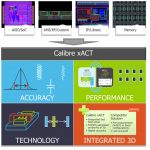

Calibre xACT Shakes Up 16nm and Below Extraction Game

Mentor Graphics made a big announcement regarding SOC extraction at their User2User conference in San Jose during April. Before I get to the meat of the announcement, I’d like to reflect back on the early days of Calibre-DRC at Mentor. I was in Sales at Mentor around 1999, and Calibre-DRC was the new kid on the block. We had to go convince… Read More

Are There Trojans in Your Silicon? You Don’t Know

Yesterday was the Mentor users’ group U2U. As usual, Wally Rhines gave the keynote, this year entitled Secure Silicon, Enabler for the Internet of Things. Wally started off saying it was a challenge to find a new angle. The number of news articles on cloud computing has exploded from nothing to 72,000 last year. On IoT from … Read More