Verification as an effectively unbounded problem will always stir debate on ways to improve. A natural response is to put heavy emphasis on making existing methods faster and more seamless. That’s certainly part of continuous improvement but sometimes we also need to step back and ask the bigger questions – what is sufficient … Read More

Tag: machine learning

EDA Powered by Machine Learning panel, 1-on-1 demos, and more!

DAC is upon us again! The Design Automation Conference holds special meaning to me as it was the first technical conference I attended as a semiconductor professional, or professional anything for that matter. That was 33 years ago and I have not missed one since. This year my wife and I both will be walking the DAC floor and it would… Read More

We Need Libraries – Lots of Libraries

It was inevitable that machine learning (ML) would come to EDA. In fact, it has already been here a while in Solido’s variation tools. Now it has found an even more compelling application – library characterization. Just as ML has radically transformed other computational arenas; it looks like it will be extremely disruptive here… Read More

Lip-Bu on Opportunity

Given a chance to talk with someone as connected as Lip-Bu Tan (President and CEO of Cadence and Chairman of the VC firm Walden International), it is tempting to ask all the usual questions about industry growth and directions in cloud, automotive, IIoT, AI and so on. I wanted to try something different. If you make a living (or plan… Read More

NetSpeed Taking a Ride with Autonomous Automobiles

The push for autonomous automobiles continues at a rapid pace. Last week a new conference was held in Santa Clara, CA by the Linley Group focused on Autonomous Hardware. The group included presentations from GLOBAL FOUNDRIES, Synopsys, NetSpeed Systems, Arteris, EMBC, Cadence, CEVA, ARM and Trilumina covering ADAS and autonomous… Read More

Machine Learning and EDA!

Semiconductor design is littered with complex, data-driven challenges where the cost of error is high. Solido’s new ML (machine learning) Labs, based on Solido’s ML technologies developed over the last 12 years, allows semiconductor companies to collaboratively work with Solido in developing new ML-based EDA products.

Data… Read More

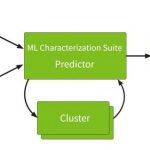

Machine Learning Accelerates Library Characterization by 50 Percent!

Standard cell, memory, and I/O library characterization is a necessary, but time-consuming, resource intensive, and error-prone process. With the added complexity of advanced and low power manufacturing processes, fast and accurate statistical and non-statistical characterization is challenging, creating the need … Read More

A Formal Feast

It’s not easy having to deliver one of the last tutorials on the last day of a conference. Synopsys drew that short straw for their tutorial on formal methodologies at DVCon this year. Despite that they delivered an impressive performance, keeping the attention of 60 attendees who said afterwards it was excellent on technical content,… Read More

ARMing AI/ML

There is huge momentum building behind AI, machine learning (ML) and deep learning; unsurprisingly ARM has been busy preparing their own contribution to this space. They announced this week a new multi-core micro-architecture called DynamIQ, covering all Cortex-A processors, whose purpose is in their words, “to redefine … Read More

Machine Learning for Dummies

I write a lot about data-driven algorithms, in particular those informed by Machine Learning. I thought it would be nice to give the low-down on machine learning for the uninitiated. Below, I discuss four essential questions. The answers are based, in part, from a recent discussion with Pedro Domingos, author of The Master Algorithm… Read More