In a presentation at the RISC-V Summit North America 2025, John Simpson, Senior Principal Architect at SiFive, delved into the evolving landscape of RISC-V extensions tailored for artificial intelligence and machine learning. RISC-V’s open architecture has fueled its adoption in AI/ML markets by allowing customization… Read More

Tag: machine learning

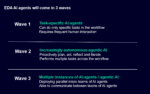

EDA AI agents will come in three waves and usher us into the next era of electronic design

Author: Niranjan Sitapure, AI Product Manager, Siemens EDA

We are at a pivotal point in Electronic Design Automation (EDA), as the semiconductors and PCB systems that underpin critical technologies, such as AI, 5G, autonomous systems, and edge computing, grow increasingly complex. The traditional EDA workflow, which includes… Read More

CEO Interview: Sean Park of Point2 Technology

Sean Park is a seasoned executive with over 25 years of experience in the semiconductors, wireless, and networking market. Throughout his career, Sean has held several leadership positions at prominent technology companies, including IDT, TeraSquare, and Marvell Semiconductor. As the CEO, CTO, and Founder at TeraSquare,… Read More

Elevating AI with Cutting-Edge HBM4 Technology

Artificial intelligence (AI) and machine learning (ML) are evolving at an extraordinary pace, powering advancements across industries. As models grow larger and more sophisticated, they require vast amounts of data to be processed in real-time. This demand puts pressure on the underlying hardware infrastructure, particularly… Read More

Emotion AI: Unlocking the Power of Emotional Intelligence

Emotion AI, also known as affective computing or artificial emotional intelligence, is a rapidly growing field within artificial intelligence that seeks to understand, interpret, and respond to human emotions. This technology is designed to bridge the gap between human emotions and machine understanding, enabling more … Read More

Mitigating AI Data Bottlenecks with PCIe 7.0

During a recent LinkedIn webcast, Dr. Ian Cutress, Chief Analyst at More than Moore and Host at TechTechPotato, and Priyank Shukla, Principal Product Manager at Synopsys, shared their thoughts regarding the industry drivers, design considerations, and critical advancements in compute interconnects enabling data center… Read More

RAAAM Memory Technologies ay the 2024 Design Automation Conference

This is the first year that RAAAM is attending DAC and presenting its revolutionary on-chip memory technology. Remember, DAC is the #1 EDA networking event where new technologies are often launched and this is one of many examples for #DAC2024.

Modern chips in various applications, such as Artificial Intelligence (AI) and Machine… Read More

The Fallacy of Operator Fallback and the Future of Machine Learning Accelerators

As artificial intelligence (AI) and machine learning (ML) models continue to evolve at a breathtaking pace, the demands on hardware for inference and real-time processing grow increasingly complex. Traditional hardware architectures for acceleration are proving inadequate to keep up with these rapid advancements in ML … Read More

CEO Interview: Ganesh Verma, Founder and Director of MoogleLabs

A thought leader with demonstrated history in multiple roles- project life cycles, ideation, implementation, and closing projects delivering business value and delighting stakeholders, crafting technical aspects of the company’s strategy for aligning with the business goals perfectly, discovering and implementing … Read More

Measuring Local EUV Resist Blur with Machine Learning

Resist blur remains a topic that is relatively unexplored in lithography. Blur has the effect of reducing the difference between the maximum and minimum doses in the local region containing the feature. Blur is particularly important for EUV lithography since EUV lithography is prone to stochastic fluctuations and also driven… Read More