Power in IoT edge devices gets a lot of press around how to make devices last for years on a single battery charge, significantly through “dark silicon” – turning on only briefly to perform some measurement and shoot off a wireless transmission before turning off again. But we tend to forget that the infrastructure to support… Read More

Tag: low power

Analog, Low-power Optimization at SMIC

Talking with actual IC designers is always fascinating to me, because these engineers are the unsung heroes that enable our modern day world of consumer and industrial electronics. Too often we only hear from the CEO or other C-level executives in the press about their own companies, products, services and vision. I recently had… Read More

Dolphin Webinar “The proven recipe for uLP SoC”

Dolphin will hold a live webinar on November 15, 9:00 AM PST or November 22, 10:00 AM GMT. This webinar targets the SoC designers wanting to learn how to quickly implement ultra-low power (uLP) techniques, using proven recipes.… Read More

RRAM Redux

Advanced memory technologies are a perennially hot topic thanks to a proliferation of data-hungry applications pushing our demand for more capacity and performance at less power and area. Among several technology contenders is Resistive RAM or RRAM (also called ReRAM). In this technology a conducting filament is grown through… Read More

Achieving Lower Power through RTL Design Restructuring (webinar)

From a consumer viewpoint I want the longest battery life from my electronic devices: iPad tablet, Galaxy Note 4 smart phone, Garmin Edge 820 bike computer, and Amazon Kindle book reader. In September I blogged about RTL Design Restructuring and how it could help achieve lower power, and this month I’m looking forward to … Read More

Low power physical design in the age of FinFETs

Low power is now a goal for most digital circuit designs. This is to reduce costs for packaging, cooling, and electricity; to increase battery life; and to improve performance without overheating. I talked to the experts on physical design for ultra-low power at Mentor Graphics recently about the challenges to P&R tools and… Read More

16nm HBM Implementation Presentation Highlights CoWoS During TSMC’s OIP

Once a year, during the TSMC’s Open Innovation Platform (OIP) Forum you can expect to see cutting edge technical achievements by TSMC and their partners. This year was no exception, with Open-Silicon presenting its accomplishments in implementing an HBM reference design in 16nm. It’s well understood that HBM offers huge benefits… Read More

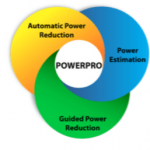

Mentor Webinar on Power Exploration for Optimizing Power

There are a lot of clever techniques to automatically find and even implement methods for register gating and memory gating, but the bulk of power-saving still depends on designer and architect insight based on expected range of use of a device, complemented by practical use-case simulations. Of course this team needs to be able… Read More

Low Power Design – a Server Perspective (Webinar)

Most of what you have read about design for low power has probably focused on mobile devices where power consumption constraints tend to outweigh performance objectives. These devices use aggressive power switching strategies, based on the reasonable assumption that parts or all of the device can be powered down at any given … Read More

Getting Low Power Design Right in Mixed Signal Designs

Mixed-signal design creates all sorts of interesting problems for implementation and verification flows, particularly when it comes to design for low power. We tend to think of mixed-signal as a few blocks like PLLs, ADCs and PHYs on the periphery of the design. Constrain and verify the digital power requirements up to analog … Read More