Clock gating is arguably the mostly widely-used design method to reduce power since it is broadly applicable even when more sophisticated methods like power islands are ruled out. But this style can be fraught with hazards even for careful designers. When you start with a proven-correct logic design and add clock gating, the logic… Read More

Tag: low power

Accurate Power Sooner

Synopsys PrimeTime PX, popularly known as PT-PX, is widely recognized as the gold standard for power signoff. Calculation is based on a final gate-level netlist reflecting final gate selections and either approximate interconnect parasitics or final parasitics based on the post-layout netlist. The only way to get more accurate… Read More

Design Deconstruction

It is self-evident that large systems of any type would not be possible without hierarchical design. Decomposing a large system objective into subsystems, and subsystems of subsystems, has multiple benefits. Smaller subsystems can be more easily understood and better tested when built, robust 3[SUP]rd[/SUP] party alternatives… Read More

Active Voice

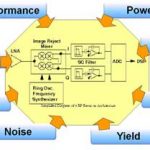

Voice activated control, search, entertainment and other capabilities are building momentum rapidly. This seems inevitable – short of Elon Musk’s direct brain links, the fastest path to communicate intent to a machine is through methods natural to us humans: speech and gestures. And since for most of us speech is a richer… Read More

RTL Correct by Construction

Themes in EDA come in waves and a popular theme from time to time is RTL signoff. That’s a tricky concept; you can’t signoff RTL in the sense of never having to go back and change the RTL. But the intent is still valuable – to get the top-level or subsystem-level RTL as well tested as possible, together with collateral data (SDC, UPF, etc)… Read More

Webinar – Low Power Circuit Sizing for IoT

Optimizing analog designs has always been a difficult and tricky process. Designing for IoT applications has only made this more difficult with the added importance of minimizing power. Unlike other circuit parameters, it is not easy to specify power as a design goal when using equations. Power is a resultant property and must… Read More

When is "off" not really off?

With the old fashioned on-off power switch came certainty of power consumption levels. This was fine back in the days before processor controlled appliances and devices. On was on and off was off: full current or no current. With the first personal computers you always had to wait for the boot process to complete before you could … Read More

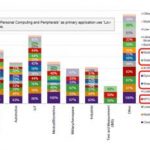

SRAM Optimization Saves Power on SOC’s and in Systems

Mobile device designers face the dilemma of reducing power and at the same time maintaining or increasing performance. Consumers will not tolerate increased battery life at the expense of performance. If it were otherwise, designers could simply dial back clock rates. Without this simple cure, the best way to reduce power for… Read More

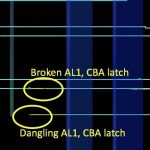

Recipes for Low Power Verification

Synopsys hosted a tutorial on verification for low power design at DVCon this year, including speakers from Samsung, Broadcom, Intel and Synopsys. Verification for low power is a complex and many-faceted topic so this was a very useful update. There is a vast abundance of information in the slides which I can’t hope to summarize… Read More

Zero Power Sensing

We’ve become pretty good at reducing power in IoT edge devices, to the point that some are expected to run for up to 10 years on a single battery charge. But what if you wanted to go lower still or if, perhaps, your design can’t push power down to a level that would meet that goal? One area in systems where it can be challenging to further … Read More