Two conferences on 3D, one just over and one coming up next week. The one that was just over was hosted by Georgia Tech, the 3rd Annual Global Interposer Technology Workshop (GIT). I wasn’t there but my ex-colleague from VLSI Technology Herb Reiter was. Herb has become very much associated with all things 3D since he led the … Read More

Tag: interposer

Xilinx and TSMC: Volume Production of 3D Parts

A couple of weeks ago, Xilinx and TSMC announced the production release of the Virtex-7 HT family, the industry’s first heterogeneous 3D ICs in production. With this milestone, all Xilinx 28nm 3D IC families are now in volume production. These 28nm devices were developed on TSMC’s Chip-on-Wafer-on-Substrate (CoWoS)… Read More

GlobalFoundries and ARM

GlobalFoundries had several interesting things at the ARM TechCon last week. Firstly, GlobalFoundries won the best in show award in the chip design category recognizing the best-in-class technologies introduced since the last TechCon.

Earlier in the summer GlobalFoundries and ARM announced the ARM Cortex-A12 processor,… Read More

3DIC, the World Goes to…Burlingame

For the tenth year, the big 3DIC conference takes place in the Hyatt Regency at Burlingame (just south of San Francisco Airport). Officially it is 3D Architectures for Semiconductor Integration and Packaging or ASIP. This year there have already been some significant 3D announcements: TSMC’s 3D program, and Micron’s… Read More

3D: the Backup Plan

With the uncertainties around timing of 450mm wafers, EUV (whether it works at all and when) and new transistor architectures it is unclear whether Moore’s law as we know it is going to continue, and in particular whether the cost per transistor is going to remain economically attractive especially for consumer markets … Read More

SEMICON Taiwan 3D

SEMICON Taiwan is September 3rd to 6th in TWTC Nangang Exhibition Hall. Just as with Semicon West in July in San Francisco, there is lots going on. But one special focus is 3D IC. There is a 3DIC and substrate pavilion on the exhibit floor and an Advanced Packaging Symposium. Design tools, manufacturing, packaging and testing solutions… Read More

Moore, or More Than Moore?

Yesterday was the 2013 GSA Silicon Summit, which was largely focused on contrasting what advances in delivering systems will depend on marching down the ladder of process nodes, and which will depend on innovations in packaging technology. So essentially contrasting Moore’s Law with what has come to be known as More Than… Read More

3D IC: Are We There Yet?

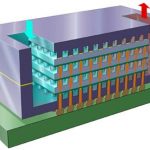

For the last few years, thru silicon via (TSV) based ICs have been looming in the mist of the future. Just how far ahead are they? Xiliinx famously has a high-end gate-array in production on a 2.5D interposer, Micron has a memory cube, TSMC has done various things in 3D that it calls CoWoS (chip on wafer on substrate), Qualcomm have been… Read More

Cadence 3D Methodology

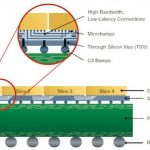

A couple of weeks ago was the 3D Architectures for Semiconductor Integration and Packagingconference in Redwood City. Cadence presented the changes that they have been making to their tool flow to enabled 2.5D (interposer-based) and true 3D TSV-based designs. You know what TSV stands for by now right? Through-silicon-via, … Read More

3D Architectures for Semiconductor Integration and Packaging

There is obviously a lot going on in 3D IC these days. And I don’t mean at the micro level of FinFETs which is also a way of going vertical. I mean through-silicon-via (TSV) based approaches for either stacking die or putting them on an interposer. Increasingly the question is no longer if this technology will be viable (there… Read More