You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Next week it is Semicon West in the Moscone Center from Tuesday to Thursday, July 10-12th. Cadence will be on a panel session during a session entitled The 2.5D and 3D packaging landscape for 2015 and beyond. This starts with 3 short keynotes:

- 1.10pm to 1.25pm: Dr John Xie of Altera on Interposer integration through chip on wafer on

…

Read More

Cadence/TSMC 3Dby Paul McLellan on 06-11-2012 at 5:16 pmCategories: Cadence, EDA

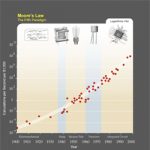

Mark Twain remarked that everyone talks about the weather but nobody does anything about it. 3D ICs seems to be a bit like that. Over the last couple of years there have been lots of people talking about 3D but very little that has actually been manufactured. In addition to the weather, everyone talks about Xilinx’s 3D Virtex… Read More

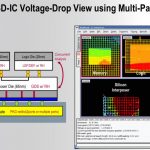

For many, maybe most, big designs, Apache’s RedHawk is the signoff tool for analyzing issues around power: electromigration, power supply droop, noise, transients and so on. But the latest designs have some issues: they are enormous (so you can’t just analyze them naively any more than you can run a Spice simulation… Read More

At the GSA 3D IC working group meeting, Cadence presented their perspective on 3D ICs. Their view will turn out to be important since the new chair of the 3D IC working group is going to be Ken Potts of Cadence. Once GSA decided the position could not be funded then an independent consultant like Herb Reiter had to bow out and the position… Read More

EDPS: 3D ICs, part IIby Paul McLellan on 04-12-2012 at 10:00 pmCategories: EDA, Events

Part I is here.

In the panel session at EDPS on 3D IC a number of major issues got highlighted (highlit?).

The first is the problem of known-good-die (KDG) which is what killed off the promising multi-chip-module approach, perhaps the earliest type of interposer. The KDG problem is that with a single die in a package it doesn’t… Read More

EDPS: 3D ICs, part Iby Paul McLellan on 04-10-2012 at 10:00 pmCategories: EDA, Events

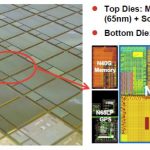

The second day (more like a half-day) of EDPS was devoted to 3D ICs. There was a lot of information, too much to summarize in a few hundred words. The keynote was by Riko Radojcic of Qualcomm, who has been a sort of one-man-band attempting to drive the EDA and manufacturing industries towards 3D. Of course it helps if you don’t … Read More

And no red and green glasses required.

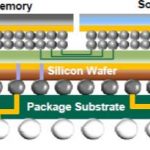

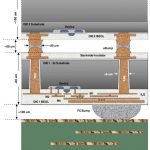

I remember the first time I heard about a Through Silicon Via (TSV), punching a hole through the entire wafer to make an electrical connection at the back, like we do all the time in printed circuit boards with through plated holes. I thought someone was trying one on and trying to make me look a fool.… Read More

3D Standardsby Paul McLellan on 02-01-2012 at 5:06 pmCategories: Ansys, Inc., EDA

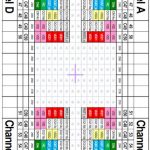

At DesignCon this week there was a panel on 3D standards organized by Si2. I also talked to Aveek Sarkar of Apache (a subsidiary of Ansys) who is one of the founding member companies of the Si2 Open3D Technical Advisory Board (TAB), along with Atrenta, Cadence, Fraunhofer Institute, Global Foundries, Intel, Invarian, Mentor, Qualcomm,… Read More

The ASIC business is getting more and more complicated. The ability to produce innovative die at a competitive price to solve increasingly complex problems just isn’t enough. The technology required to package that die is now front and center.

Here, at the junction of advanced design, process technology and state-of-the art … Read More

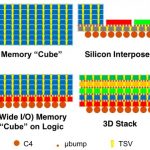

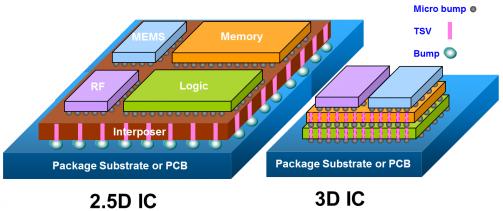

3D and 2.5D (silicon interposer) designs create new challenges for EDA. Not all of them are in the most obvious areas. Mentor has an interesting presentation on what is required for verification and testing of these types of designs. Obviously it is somewhat Mentor-centric but in laying out the challenges it is pretty much agnostic.… Read More