The first transistor was made of two electrodes, held in place by plastic, making contact with a piece of doped germanium. Ever since then, devices and their packaging have been performing a complicated and oftentimes intricate dance. Single transistor devices became integrated circuits, and along the way separate IC’s were… Read More

Tag: interposer

16nm HBM Implementation Presentation Highlights CoWoS During TSMC’s OIP

Once a year, during the TSMC’s Open Innovation Platform (OIP) Forum you can expect to see cutting edge technical achievements by TSMC and their partners. This year was no exception, with Open-Silicon presenting its accomplishments in implementing an HBM reference design in 16nm. It’s well understood that HBM offers huge benefits… Read More

Foundry Technology Packaging Solutions

A significant shift is underway in the fabless semiconductor business model. As the application markets have become more diverse (and more cost-sensitive), product requirements have necessitated a new focus on multi-die packaging technology. … Read More

How HBM Will Change SOC Design

High Bandwidth Memory (HBM) promises to do for electronic product design what high-rise buildings did for cities. Up until now, electronic circuits have suffered from the equivalent of suburban sprawl. HBM is a radical transformation of memory architecture that will have huge ripple effects on how SOC based electronics are … Read More

TSV Modeling Key for Next Generation SOC Module Performance

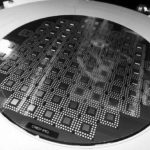

The use of silicon interposers is growing. Several years ago Xilinx broke new ground by employing interposers in their Virtex®-7 H580T FPGA. Last August Samsung announced what they say is the first DDR4 module to use 3D TSV’s for enterprise servers. Their 64GB double data rate-4 modules will be used for high end computing where … Read More

EDPS: Fins and FinFETs

Look at those dolphins with fins on their backs. Did you know that FinFETs are actually named after them since Chenming Hu and his team though that they looked like a fish’s fin? And since they invented FinFETs they got to name them too. But those dolphins also mean that it is nearly time for this years Electronic Design Process… Read More

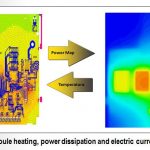

ANSYS Talks About Multi Physics for Thermal Analysis at DesignCon

ANSYS makes a big deal of being a multi-physics company. Still it has taken them a while to fully integrate Apache. Nevertheless it seems like there is a compelling argument for combining technologies to solve SOC design problems. Frankly most chip designers would be hard pressed to think of a reason for using computational fluid… Read More

FD-SOI, FinFET, 3D in Monterey

Last night the IEEE Silicon Valley Chapter had a panel session that was in some ways a preview of some of what will be discussed at the Electronic Design Process Symposium in Monterey next Thursday and Friday. At EDPS Herb Reiter organized a session on FinFET, 3DIC and FD-SOI (sort of how many buzzwords can you get into one set of titles).… Read More

TSMC: 3D, 450mm, CoWoS and More

The first keynote at the Burlingame 3D conference was by Doug Yu of TSMC. Not surprisingly he was talking about 3D. In particular, TSMC has WLSI technology that they call CoWoS, which stands for chip-on-wafer-on-substrate which pretty much describes how it is built. This is the technology that Xilinx uses for its recently announced… Read More

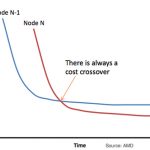

AMD Goes 3D

I attended the 3D packaging conference in Burlingame this week. The most interesting presentation to me was by Bryan Black of AMD. He argued very convincingly that Moore’s Law is basically over for the PC microprocessor business and the way forward is going to be 3D. AMD are clearly working on all this.

Increased density and… Read More