Almost without exception these days, semiconductor products face strict power and thermal budgets. Of course there are many issues with dynamic power but one big area that has been getting increasingly problematic is static power. For various technical reasons we can no longer reduce the voltage as much as we would like from one… Read More

Tag: fpga

FPGAs The Life Savers

Silicon dominates our lives, CPU’s, GPU’s are in the limelight but the unsung hero is the FPGA. They simply do the work where other silicon dare not tread, as they are unfit for the task. Never send a boy to do a man’s job.

For a moment, if we can, just for a few minutes perhaps we can break away from the social media bubble… Read More

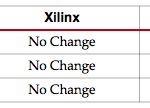

Coke vs. Pepsi; Xilinx vs. Altera

I have many thoughts on this topic, so forgive the word salad that may ensue. I have been thinking about Coca-Cola lately, partly because I bought an old coke machine (I’m one of those guys… pray for my wife). I am amazed that Coke which was founded in 1886, still has a secret recipe. I like that, but boy every time the web reveals the coke… Read More

The fixed and the finite: QoR in FPGAs

There is an intriguingly amorphous term in FPGA design circles lately: Quality of Results, or QoR. Fitting a design in an FPGA is just the start – is a design optimal in real estate, throughput, power consumption, and IP reuse? Paradoxically, as FPGAs get bigger and take on bigger signal processing problems, QoR has become a larger… Read More

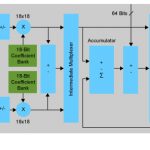

Remember FPGA Memory

We must admit the excitement of the FinFETs and all that coupled with the enormous amount of DSPs and BRAMs in the FPGA world is very cool. They even have ARMs, and I highly recommend that they get Legs then they can run around and everything and fit in with the rest of us. Perhaps the Feds can grant them immigration status and they could… Read More

Missed #50DAC? See Aldec Verification Sessions Online

Aldec, Inc. is an industry-leading Electronic Design Automation (EDA) company delivering innovative design creation, simulation and verification solutions to assist in the development of complex FPGA, ASIC, SoC and embedded system designs. With an active user community of over 35,000, 50+ global partners, offices worldwide… Read More

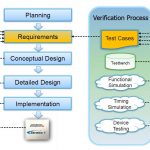

It’s all in the details of FPGA requirements management

Word association: if I said “requirements management”, you’d probably say IBM Rational “DOORS,” or maybe Serena or Polarion if you come from the IT world. But what if the requirements you need to manage are for an FPGA or ASIC, with HDL and testbench code and waveform files and more details backing verification, and compliance… Read More

Are there enough FPGA tools?

Sometimes I send my boy to grab me a tool and hours later he comes back with the wrong one. The patient man that I am, I calmly explain what I mean and then the world is right once more. Believe that do ya?

As you know the world is flooded with tools, tools and more tools. We all have our ruts and favorite flows and such but given the huge FPGA … Read More

Wireless Algorithm Validation from System to RTL to Test

This year’s #50DAC will be chock-full of technical content because that is what attracts the masses of semiconductor professionals, like moths to a flame, or like me to a Fry’s Electronics store. Interesting note, I went to high school with Randy Fry. His Dad started the Fry’s supermarket chain which he sold… Read More

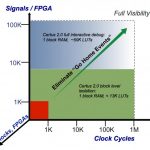

Accelerating Design Debug in an ASIC Prototype

ASIC prototyping in FPGAs is starting to trend on SemiWiki. As FPGA technology becomes more advanced customers tell me that the traditional debug tools are inadequate. Faced with the very restrictive debugging capabilities and very long synthesis/place/route times the debugging cycle in these prototype platforms are quite… Read More