Has your wife ever said “Your name, I’m not a computer”? Well maybe mine has. I know what you are thinking… This guy is married? Yup, I over achieved too. Have child #7 on the way Lord willing, so you probably guessed I don’t follow much of the world’s planning and such. Like you, no one in my house really understands what I do, nor cares … Read More

Tag: fpga

Gigahertz FFT rates on a 500MHz budget

A basic building block of any communication system today is the fast Fourier transform, or FFT. A big advantage of FPGA implementations of FFTs is they can be scaled and tuned for the task at hand, optimizing data flow, resource use, and power consumption. Scaled, that is, up to the clock speed of the FPGA – or so it would seem.

Today’s… Read More

A bird told me the EDPS Monterey Conference was a great success

The 20th annual Electronic Design Process Symposium (EDPS) held April 18-19 at the Monterey Beach Hotel in Monterey California was an unqualified success. I know this because a bird (seagull?) sitting on the window sill of the conference room was so captivated by the fascinating insight provided by a number of luminaries that … Read More

FPGAS – The New Single Board Computers?

I have always felt that FPGAs have been the red haired step child of Silicon Valley. Software weenies have hated them, they are mysterious and take too long to route. Even though they can be massively parallel and the most deterministic piece of silicon you can buy besides a million dollar ASIC, the GPU steals their glory, for now. … Read More

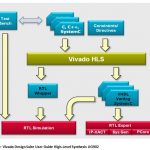

Xilinx: Hide the RTL

Tom Feist of Xilinx presented here at the GlobalPress Electronics Summit about their strategy to take design abstraction up another level. In the SoC world, we are still pretty much stuck at the RTL level and have moved to higher abstractions by using an IP strategy. But at least all IC designers are RTL-literate.

Xilinx, in the Vivado… Read More

Altera, Intel, TSMC, ARM: the Plot Thickens

Vince Hu of Altera presented us her at the GlobalPress Electronics Summit on their process roadmap. Since just a month or two ago they announced that Intel would be their foundry at 14nm, everyone wanted to get a better idea of what was really going on.

At 28nm, Altera use 2 processes, TSMC 28HP (for high end Stratix-5 devices) and TSMC… Read More

Webinar: Making a Simple, Structured and Efficient VHDL Testbench

Most simple testbenches have close to no structure, are terrible to modify and hopeless to understand. They often take far too much time to implement and provide close to no support when debugging potential problems. This webinar will demonstrate how to build a far better testbench with respect to all these issues – in significantly… Read More

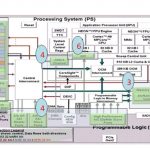

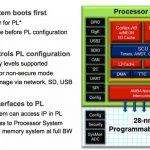

Ivo Bolsens’ Keynote on the All-Programmable SoC

Ivo Bolsens, the CTO of Xilinx, is giving the opening keynote at the Electronic Design Process Symposium (EDPS) in Monterey on Thursday and Friday this coming week. The title of his keynote is The All Programmable SoC – At the Heart of Next Generation Embedded Systems. He covers a lot of ground but the core of his presentation… Read More

High Level Synthesis – It’s for Real

It was spring 2010 and I was asked to attend an HLS (High Level Synthesis) meeting. To be honest I cringed, after my bad relationship with Accel DSP and broken promises my heart was all walled up and needed counseling. But my management had a way of making me an offer I could not refuse, like keeping my job. So reluctantly I went. Does your… Read More

RTDA at Altera

I talked to Yaron Kretchmer of Altera to find out how they are using RTDA’s products. I believe that Altera are the oldest customer of RTDA, dating back over 15 years, originally used by the operations team around the test floor before propagating out in the EDA and software worlds more recently.

Altera use two RTDA tools, LicenceMonitor… Read More