At the recent Semicon West, Michel Haond of ST Microelectronics had a presentation on 14nm FD-SOI, or what they more lengthily call UTBB FD-SOI (which when you expand it all out comes to Ultra Thin Body and Buried-Oxide Fully Depleted Silicon on Insulator). When Chenming Hu (or whoever in his group) came up with the term FinFET it … Read More

Tag: finfet

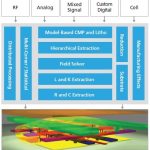

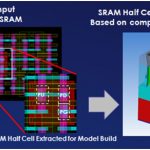

A Deeper Insight into Quantus QRC Extraction Solution

Last month Cadenceannounced its fastest parasitic extraction tool (minimum 5 times better performance compared to other available tools) which can handle growing design sizes with interconnect explosion, number of parasitics and complexities at advanced process nodes including FinFETs, without impacting accuracy of … Read More

Intel Versus TSMC 14nm Processes

Intel has begun to release some details on their 14nm process. I thought it would be interesting to contrast what Intel has disclosed to TSMC’s 16nm process disclosure from last year’s IEDM (TSMC calls their 14nm process 16nm).

[TABLE] align=”center” border=”1″

|-

| style=”width: 141px”… Read More

What Comes After FinFET?

So what comes after FinFETs? At 14/16nm (or 22nm if you are Intel) we had FinFET transistors, where the channel was no longer planar but stuck out of the wafer vertically, and the gate wrapped around it on 3 sides. The key thing that made FinFET transistors attractive was that the channel was thin so that the gate controlled it well. … Read More

FD-SOI: 20nm Performance at 28nm Cost

There has been a lot of controversy about whether FD-SOI is or is not cheaper to manufacture than FinFET. Since right now FinFET is a 16nm process (22nm for Intel) and FD-SOI is, for now, a 28nm process it is not entirely clear how useful a comparison this is. Scotten Jones has very detailed process cost modeling software (that is what… Read More

Taking a leap forward from TCAD

We all know that Technology Computer Aided Design (TCAD) simulations are essential in developing processes for semiconductor manufacturing. From the very nature of these simulations (involving physical structure and corresponding electrical characteristics of a transistor or device), they are predominantly finite-element… Read More

Xilinx: Revenue Down, Profit Up, FinFET on Schedule

Xilinx announced their results today and had their conference call this afternoon, which I listened to. For them this is 1Q fiscal 2015 which means you have to be careful since there is a big difference between talking about fiscal quarters and calendar quarters. Xilinx’s conference calls are interesting for a couple of … Read More

Setting the Record Straight on FD-SOI Costs

I recently published an article on Semiwiki “Is SOI Really Less Expensive”. That article was the result of months of careful research and analysis. I looked at planar FDSOI versus bulk planar, bulk FinFETs and FinFETs on SOI at three different nodes. I took a consistent set of assumptions with respect to the fab used to run the processes,… Read More

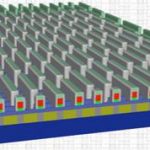

New Release of Semulator3D at #semiconwest

One of Coventor’s flagship products is SEMulator3D, and at Semicon West they announced a new version, 2014.100.

SEMulator3D is a powerful 3D semiconductor and MEMS process modeling platform. It uses highly efficient physics-driven voxel modeling technology. It models the physical effects of process steps, which is… Read More

Keywords: FD-SOI, Cost, FinFET

How to synthesize a pretty good article Is SOI Really Less Expensive, and even more important the impressive amount of comments (56) generated? Let’s start with the initial article. Pretty good, but slightly biased, when you carefully dissect it, like I did in one of the comments (you can find it in-extenso at the end of this post).… Read More