Several months ago we had suggested that we were concerned that Apple’s A9 processor would wind up being 20nm planar (maybe 14nm planar) rather than the expected 14nm FinFET. As we are now under 9 months from a likely launch time for Apple’s next gen IPhone the timing for getting a 14nm FinFET processor on board the phone… Read More

Tag: finfet

Coventor Panel at IEDM Digs into Variation Issues

Recently I attended a panel discussion on variability in semiconductor fabrication hosted by Coventor in conjunction with the IEEE IEDM conference in San Francisco. The IEEE bills the conference as “the world’s pre-eminent forum for reporting technological breakthroughs in the areas of semiconductor and electronic device… Read More

IEDM Advanced CMOS Technology Platform Session

First I want recognize that IEDM once again provided all of the attendees with the proceedings as soon as we arrived at the conference, in fact the proceeding included every year of IEDM back to 1955. This is how a conference should be run! Anyone who read my blog about the SPIE Advanced Lithography Conference will know how frustrating… Read More

ANSYS Updates RedHawk for FinFET Nodes

Most designers are not using FinFETs yet, however the increased transistor density and power advantages they offer are compelling. Smaller feature sizes have been a consistent driver in semiconductor technology. Eventually the market will move more and more to FinFET processes, increasingly leaving behind planar transistors.… Read More

Jean-Louis Gassée on Intel and Mobile

I came across a very interesting article/blog written over the weekend by Jean-Louis Gassée on Intel and mobile. It covers some similar ground to several of my blog posts on the topic but also has some new facts. And it has additional credibility since Jean-Louis was head of product development and worldwide marketing at Apple (pre-iPhone).… Read More

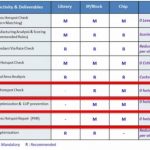

Design Rule Checking (DRC) Meets New Challenges

The traditional batch-oriented DRC process run as a final check to ensure compliance with foundry yield goals is quickly moving toward a concurrent DRC process performed early and often throughout design, especially at the 28 nm and smaller process nodes. What are the technology factors causing this change?

- Increasing number

Intel 2014 Investor Meeting and 14nm Status

Intel’s investor meeting was held yesterday and for me the presentation that is most interesting is Bill Holt’s. The presentations are available on the Intel website: Intel Corporation – Presentations Material 2014. Here is the 2013 version of this presentation: Intel Corporation – Presentations Materials 2013… Read More

IEDM 2014 Preview

The International Electron Devices Meeting (IEDM) is one of the premier conferences for the presentation of the latest semiconductor processes and process technologies. IEDM is held every year in December alternating between San Francisco and Washington DC. This year IEDM will be held at the San Francisco Hilton on December… Read More

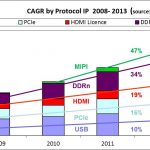

IP-SoC 2014 Top Class Presentations…

… were given to an ever shrinking audience. This is IP-SoC paradox: audience has enjoyed very good presentations made by Cadence, Synopsys or ST-Microelectronic, to name just a few. As far as I am concerned, I was happy to present the “Interface IP Winners and Losers (Protocols)” in the amphitheater during the first day, enjoying… Read More

In-Design DFM Signoff for 14nm FinFET Designs

While FinFET yield controversy is going on, I see a lot being done to improve that yield by various means. One prime trend today, it must be, it’s worthwhile, is to pull up various signoffs as early as possible during the design cycle. And DFM signoff is a must with respect to yield of fabrication. This reminds me about my patents filed… Read More