You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Richard Goering is well-known from his editorial days at EE Times (going back some 25 years), now at Cadence he blogs at least once a week on EDA topics that touch Cadence tools.

Before DAC he talked with Srinath Anantharaman about how Cadence tools work together with ClioSoft tools to keep IC Design Data Management Simple.

Through… Read More

The next Apache webinar is coming up on 21st July at 11am Pacific time on “IP integration methodology”.

This webinar will be conducted by Arvind Shanmugavel, Director Applications Engineering at Apache Design Solutions. Mr. Shanmugavel has been with Apache since 2007, supporting the RedHawk and Totem product … Read More

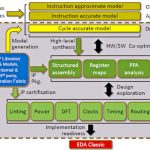

Design for test at RTLby Paul McLellan on 07-10-2011 at 3:09 pmCategories: EDA

Design for test (DFT) imposes various restrictions on the design so that the test automation tools (automatic test pattern approaches such as scan, as well as built-in self-test approaches) will subsequently be able to generate the test program. For example, different test approaches impose constraints on clock generation… Read More

Intel’s new Tri-Gate technology is causing quite a stir on the stock chat groups. Some have even said if Intel uses its Tri-Gate technology on only Intel processors ARM will be in deep deep trouble. These guys are “Intel Longs” of course and they are battling “Intel Shorts” with cut and paste news clips.

“ARM is in trouble & this… Read More

At DAC 2011 in San Diego, Apache gave many product presentations. Of course not everyone could make DAC or could make all the presentations in which they were interested. So from mid-July until mid-August these presentations will be given as webinars. Details, and links for registration, are here on the Apache website.

The seminars… Read More

During last week-end, I had the good surprise to meet with one of my oldest friend, Eric, who remind me the old time, when we were working together as ASIC designers for… a Supercomputer project.

In France, in a French company (Thomson CSF) active in the military segment and being able to spend which was at that time a fortune ($25M) … Read More

In my rush on Wednesday at DAC I had almost over-looked the last two companies I talked with: Invarian and AnaGlobe. These last two I had hand-written notes on paper, so I just got to the bottom of my inbox tonight to write up the final trip reports.

Invarian

Jens Andersen and Vladimir Schellbach gave me an overview of tools that perform… Read More

We all knew that Apache had filed for an IPO earlier and were just waiting for the timing and price to be revealed. Rumors have been circulating about an acquisition and today we know that the rumors were true asAnsys paid $310 million in cash for Apache.

Ansys stock has surged some 35% over the past twelve months:

Products

This acquisition… Read More

SOC Realizationby Paul McLellan on 06-27-2011 at 5:28 pmCategories: EDA

There are some very interesting comments to the last entry on SoC Realization and how more and more chips are actually assembled out of IP. There was clearly a lot of discussion in this area at DAC, although most people (Atrenta being an exception) don’t use the term SoC Realization, presumably because it was originated by … Read More

Introduction

Before DAC I met with Stephen Pateras, Ph.D. at Mentor Graphics, he is the Product Marketing Director in the Silicon Test Solutions group. Stephen has been at Mentor for two years and was part of the LogicVision acquisition. He was in early at LogicVision and went through their IPO, before that he was at IBM in the mainframe… Read More