You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Calypto has an interesting webinar coming up about Minimizing RTL Power Through Sequential Analysis. It is next Tuesday December 4th at 11am.

Insert standard paragraph about how power is the new timing, everyone worries about power, battery life in smartphones, half-empty datacenters.

You probably already know about clock… Read More

Since the beginning of the semiconductor industry, improving the rate of yield learning has been a critical factor in the success silicon manufacturing. Each fab has dedicated yield teams that look at the yield of wafers manufactured the previous day and attempt to find the root cause of any unexpected “excursions.” In earlier… Read More

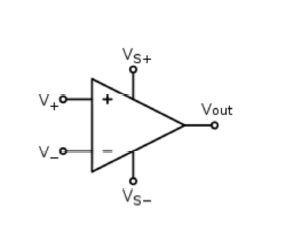

I met Frank Wiedmann on LinkedIn because we are both members of the Analog Mixed Signal group, and he has an interesting background in AMS IC design.

Since he lives in Munich we conducted our interview by email.… Read More

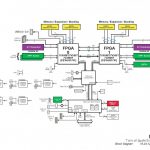

Collaboration in EDA is nothing new, however you may not be aware of how the Dini Group and Tektronix have worked together on an FPGA prototyping platform to address issues like debugging with full visibility across an entire multi-FPGA design. At SemiWiki we’ve blogged a couple of times so far about the new debug approach… Read More

Dear Santa,

It has been many years since I have written you. I was taught never to ask anyone for anything for myself, that it is a presumptuous and selfish thing to do, so this is not for me. I know you are busy filling the wish lists of children everywhere, but wanted to take a moment to ask for your help for everyone.… Read More

You often hear the mantra that Analog Mixed-Signal (AMS) behavioral models are inaccurate. It is repeated so often that it starts to morph into “AMS models are inherently inaccurate”. This is not true.

Source: Wikipedia

… Read More

A catchy phrase used by bloggers and journalists these days is “Internet of Things“, or IoT if you prefer acronyms. All of this is made possible by EDA tools in the hands of SoC designers to create useful products like my Jawbone ICON bluetooth headset. Tonight I discovered that I could customize my bluetooth headset… Read More

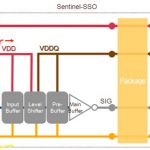

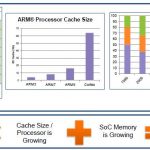

Matt Elmore has a two-part blog about the growing complexity of signal integrity analysis, both on the chip itself and the increasingly complex analysis required to make sure that signals (and power) get in and out of the chip from the board cleanly, especially to memory, which requires simultaneous analysis of chip-package-system… Read More

Electronic Design and Solutions Fair (EDSF) was held in Yokohama Japan from Wednesday to Friday last week. It was held at the Pacifico Hotel, somewhere I have stayed several times, not far from the Yokohama branch of Hard Rock Cafe and, what used to be at least, the biggest ferris-wheel in the world.

Atrenta was one of the many companies… Read More

Once upon a time, ASIC designers were integrating memories in their design (using a memory compiler being part of the design tools provided by the ASIC vendor), then they had to make the memory observable, controllable… and start developing the test program for the function, not a very enthusiastic task (“AAAA” and “5555” and other… Read More