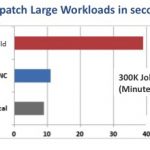

When you see a new product announcement from an EDA company, it is always put in terms that make it seem as if the engineer is sitting at his or her desktop with a big server and is running the new tool to wondrous effect. But the reality in the real world is that most companies have a computing infrastructure of server farms, often several… Read More

Tag: eda

Signoff Summit and Voltus

Yesterday Cadence had an all-day Signoff Summit where they talked about the tools that they have for signoff in advanced nodes. Well, of course, those tools work just fine in non-advanced nodes too, but at 20nm and 16nm there are FinFETs, double patterning, timing impacts from dummy metal fill, a gazillion corners to be analyzed… Read More

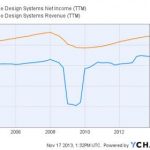

Cadence Design Systems’ Shares Are Surprisingly Cheap

In the third and final (for now) part of this series on the EDA design tool vendors, I’d like to take a closer look at Cadence Design Systems. This is probably the most interesting of the three from both an industry perspective as well as an investment perspective for a variety of reasons. With that said I’d like to first provide some … Read More

A Brief History of eSilicon

eSilicon Corporation was founded in 2000 with Jack Harding as the founding CEO and Seth Neiman of Crosspoint Venture Partners as the first venture investor and outside Board member. They both remain involved in the company today, with Jack continuing as CEO and Seth now serving as Chairman of the Board.

Both Harding and Neiman brought… Read More

Signoff Summit: The Fastest Path to Design Signoff

Cadence’s Signoff Summit will be held next week, November 21 at Cadence in San Jose.

This is the first of a series of all-day Signoff Summits from Cadence that focus on the multiple facets of design signoff. This first summit will include keynote addresses plus sessions covering the multiple solution components that comprise… Read More

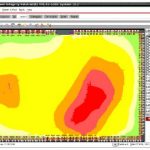

A New IC Power Integrity Tool

In EDA we have come to expect that only small start-up companies create new tools, however a team at Cadencehas developed a new IC power integrity tool called Voltus from scratch. To learn more I spoke last week with KT Moore, a Group Director at Cadence. I’ve known KT for over a decade, and first met him when he was at Magma marketing… Read More

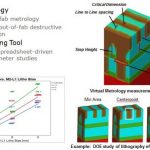

Semiconductor Fabrication Module Optimization

The growing process integration complexity at each technology node has increased development time and cost, and this trend looks to continue. There is a looming risk of delivering unrepeatable critical unit processes (or process modules) that would require revisiting development and manufacturing requalification or in … Read More

The Pelican Has Landed: Formal on an Unannounced ARM Processor

At the Jasper Users’ Group, Alex Netterville of ARM presented about how ARM are using formal on an unannounced processor code-named Pelican. Don’t read the presentation trying to find out information about Pelican itself, there isn’t any. That wasn’t the topic. Alex has been using formal approaches… Read More

Data Management in Russia

Milandr is a company based in Moscow that makes high reliability semiconductor components for the aerospace, automotive and consumer markets, primarily in Russia. They work with multiple foundries, including X-FAB and TSMC in technologies from 1um down to 65nm. Corporate headquarter and main IC design house is located in Russian… Read More

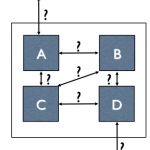

Dassault Patent on Hierarchy Management

Dassault have recently been granted a patent on their approach to managing design hierarchy. I asked them how long it took from filing the patent until it was granted and they said the whole process had taken 8 years. It is a bit of an indictment of the patent system when it takes 8 years, also known as 4 or 5 process nodes, for a patent to… Read More