In the spectrum of functional verification platforms – software-based simulation, emulation and FPGA-based prototyping – it is generally agreed that while speed shoots up by orders of magnitude (going left to right) ease of debug drops as performance rises and setup time increases rapidly, from close to nothing for simulation… Read More

Tag: debug

Getting out of DIY Mode for Virtual Prototypes

Virtual prototyping has, inexplicably, been largely a DIY thing so far. Tools and models have come from different sources with different approaches, and it has been up to the software development team to do the integration step and cobble together a toolchain and methodology that fits with their development effort.

That integration… Read More

A New Player in the Functional Verification Space

Israel has a strong pedigree in functional verification. Among others, Verisity (an early contributor to class-based testbench design and constrained random testing) started in Israel and RocketTick (hardware-based simulation acceleration), acquired more recently by Cadence, is based in Israel. So when I hear about an … Read More

Learn How to Debug UVM Test Benches Faster – Upcoming Synopsys Webinar

UVM for developing testbenches is a wonderful thing, as most verification engineers will attest. It provides abstraction capabilities, it encapsulates powerful operations, it simplifies and unifies constrained-random testing – it has really revolutionized the way we verify at the block and subsystem level.

However great… Read More

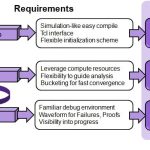

Bringing Formal Verification into Mainstream

Formal verification can provide a large productivity gain in discovering, analyzing, and debugging complex problems buried deep in a design, which may be suspected but not clearly visible or identifiable by other verification methods. However, use of formal verification methods hasn’t been common due to its perceived complexity… Read More

Mentor at DVCon – Visualize This

Steve Bailey entertained us during lunch on Tuesday with a talk on debug and visualization in the Mentor platform. Steve is based in Colorado, so had to spend the first part of his talk gloating about their Super Bowl win, but I guess he deserves that.

On a more technical note, he showed us a familiar survey they had completed with the… Read More

Multi-Level Debugging Made Easy for SoC Development

An SoC can have a collection of multiple blocks and IPs from different sources integrated together along with several other analog and digital components within a native environment. The IPs can be at different levels of abstractions; their RTL descriptions can be in different languages such as Verilog, VHDL, or SystemVerilog.… Read More

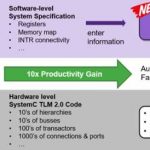

Fastest SoC time-to-success: emulators, or FPGA-based prototypes?

Hardware emulators and FPGA-based prototyping systems are descendants of the same ancestor. The Quickturn Systems Rapid Prototype Machine (RPM) introduced in May 1988 brought an array of Xilinx XC3090 FPGAs to emulate designs with hundreds of thousands of gates. From there, hardware emulators and FPGA-based prototyping … Read More

Michael Sanie Plays the Synopsys Verification Variations

I met Michael Sanie last week. He is in charge of verification marketing at Synopsys. I know him well since he worked for me at both VLSI Technology and Cadence. In fact his first job out of college was to take over support of VLSIextract (our circuit extractor), which I had written. But we are getting ahead.

Michael was born in Iran and… Read More

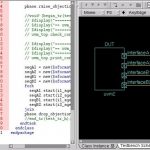

Never Imagined So Easy Class-based Testbench Debugging

When it comes to debugging a design testbench organized in object-oriented style with objects, component hierarchies, macros, transactions and so on, it becomes an onerous, tasteless, and thankless task for RTL verification engineers who generally lag in software expertise. Moreover, class-based debugging tools have lagged… Read More