Spice view of a design, block or fragment of the design is probably the lowest level of functional description of a circuit in terms of transistors, resistors, capacitors, interconnect and so on, which in several ways acts as an ultimate proof of pudding for any semiconductor design before manufacturing. However, it’s generally… Read More

Tag: concept engineering

Enabling Higher Level Design Automation with Smart Tools

Although design houses have always strived for optimizing best design flows according to their design needs by customizing the flows using effective and efficient internal as well as external tools, this need has further grown in the context of design scenarios getting wider and wider from transistor, gate and RTL to system level.… Read More

S-engine Moves up the Integration of IPs into SoCs

As the semiconductor design community is seeing higher and higher levels of abstraction with standard IPs and other complex, customized IPs and sub-systems integrated together at the system level, sooner than later we will find SoCs to be just assemblies of numerous IPs selected off-the-self according to the design needs and… Read More

Concept Engineering Showcases Effective SoC Debugging Techniques

In a complex environment of semiconductor design where an SoC can have several millions of gates and multiple number of IPs at different levels of abstractions from different sources integrated together, it becomes really difficult to understand and debug the overall SoC design. Of course, along with the SoC integration, optimization… Read More

Ten Innovative Debugging Techniques – Pre & Post Layout

In a complex world of SoCs with multi-million gates and IPs from several heterogeneous sources, verification of a complete semiconductor design has become extremely difficult, and it’s not enough. In order to ascertain the right intent of the design throughout the design cycle, debugging at various stages of the design cycle… Read More

Customization can add extraordinary power to your tool

In EDA arena we often find companies providing customization platforms along with the tools they offer to their customers. I admire such companies because they equip the end users of a tool to extend its functionality as they like according to their environment, thus increasing the designer productivity significantly. And I’m… Read More

Mark your Date for Semiconductor Design Vision

A very popular acronym is ‘WYSIWYG’ – What You See Is What You Get! This is very true and is important to visualize things to make it better in various aspects such as aesthetics, compactness, organization, structure, understandable for correction and so on; the most important, in case of semiconductor design, is being able to identify… Read More

Mixed-Signal SoC Debugging & IP Integration Made Easy

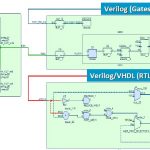

A semiconductor SoC design can have multiple components at different levels of abstractions from different sources and in different languages. While designing an SoC, IPs at different levels have to be integrated without losing the overall design goals. Of course, quality of an IP inside and outside of an SoC must be tested thoroughly.… Read More

Parasitic Debugging in Complex Design – How Easy?

When we talk about parasitic, we talk about post layout design further expanded in terms of electrical components such as resistances and capacitances. In the semiconductor design environment where multiple parts of a design from different sources are assembled together into highly complex, high density SoC, imagine how complex… Read More

What Makes A Designer’s Day? A Bottleneck Solved!

In an environment of SoCs with tough targets of multiple functionalities, smallest size, lowest power and fastest performance to achieve within a limited design cycle window in order to meet the rigid time-to-market requirements, any day spent without success becomes very frustrating for a designer. Especially during tape-out… Read More