You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

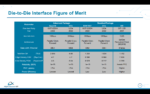

An earlier blog started with the topic of delivering 3D IC innovations faster. The blog covered the following foundational enablers for successful heterogeneous 3D IC implementation.

- System Co-Optimization (STCO) approach

- Transition from design-based to systems-based optimization

- Expanding the supply chain and tool

…

Read More

The Design Automation Conference, as always, is a good barometer on the state of EDA and my area of interest, verification. The recent DAC offered plenty of opportunities to check on trends and the status quo.

Remarkably, exhibitors and attendees were upbeat about the chip design landscape despite concerns about supply chain … Read More

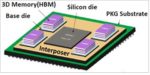

3D IC technology development started many years ago well before the slowing down of Moore’s law benefits became a topic of discussion. The technology was originally leveraged for stacking functional blocks with high-bandwidth buses between them. Memory manufacturers and other IDMs were the ones to typically leverage this … Read More

3D-ICs bring together multiple silicon dies into a single package that’s significantly larger and complex than traditional systems on a chip (SoCs). There’s no doubt these innovative designs are revolutionizing the semiconductor industry.

3D-ICs offer a variety of performance advantages over traditional SoCs. Because … Read More

The topic of chiplets is getting a lot of attention these days. The chiplet movement has picked up more momentum since Moore’s law started slowing down as process technology approached 5nm. With the development cost of a monolithic SoC crossing the $500M and wafer yields of large die-based chips dropping steeply, the decision … Read More

Discussions of chiplets has been on the rise, ever since the slowdown of Moore’s law benefits. Gartner Research projects semiconductor revenue from systems using chiplets to grow from $3.3 billion in 2020, to $50.5 billion in 2024. With any market opportunity, there are always challenges to overcome in order to realize the full… Read More

My first exposure to seeing multiple die inside of a single package in order to get greater storage was way back in 1978 at Intel, when they combined two 4K bit DRAM die in one package, creating an 8K DRAM chip, called the 2109. Even Apple used two 16K bit DRAM chips from Mostek to form a 32K bit DRAM, included in the Apple III computer, circa… Read More

One of the career Intel employees (33+ years) that Pat Gelsinger brought back is Stuart Pann. Stuart is now the Senior Vice President of the Intel Corporate Planning Group. He does not have direct foundry experience but he certainly knows Intel and Pat so it will be interesting to see where this goes.

Stuart recently penned an article… Read More

A couple of weeks ago, I blogged on GlobalFoundries’ silicon technologies supporting automotive radar applications. This time it is on GlobalFoundries’ silicon photonics technology which expects to find adoption in a broad spectrum of applications. The blog is based on listening to a technology presentation made by Dr. … Read More

Last week, Cadence hosted its annual CadenceLIVE Americas 2021 conference. Four keynotes and eighty-three different talks on various topics were presented. The talks were delivered by Cadence, its customers and partners.

One of the keynotes was from Partha Ranganathan, VP and Engineering Fellow from Google. His talk was titled,… Read More