You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Dan is joined by Krishna Settaluri, Co founder and CEO of Blue Cheetah. Krishna received his Ph.D. in electrical engineering from UC Berkeley and masters and bachelors from MIT specializing in design automation of high-speed silicon photonic links using analog generator technology. Krishna has worked at Apple, Google, Caltech… Read More

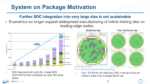

Over the recent years, the volume and velocity of discussions relating to chiplets have intensified. A major reason for this is the projected market opportunity. According to research firm Omdia, chiplets driven market is expected to be $6B by 2024 from just $645M in 2018. That’s an impressive nine-fold projected increase over… Read More

Dan and Mike are joined by Sudhir Mallya, vice president of corporate and product marketing at OpenFive. We explore 2.5D design and the role chiplets play. Current technical and business challenges are discussed as well as an assessment of how the chiplet market will develop and what impact it will have.

The views, thoughts, and

…

Read More

Earlier in April, Achronix made a product announcement with the headline “Achronix Now Shipping Industry’s Highest Performance Speedster7t FPGA Devices.” The press release drew attention to the fact that the 7nm Speedster®7t AC7t1500 FPGAs have started shipping to customers ahead of schedule. In the complex product world… Read More

In early April, Gabriele Saucier kicked off Design & Reuse’s IPSoC Silicon Valley 2021 Conference. IPSoC conference as the name suggests is dedicated to semiconductor intellectual property (IP) and IP-based electronic systems. There were a number of excellent presentations at the conference. The presentations had been… Read More

In early April, Gabriele Saucier kicked off Design & Reuse’s IPSoC Silicon Valley 2021 Conference. IPSoC conference as the name suggests is dedicated to semiconductor intellectual property (IP) and IP-based electronic systems. There were a number of excellent presentations at the conference. The presentations had been… Read More

It has been my pleasure to interview Graham Curren, CEO of Sondrel. A veteran of the Electronics Design industry, he founded Sondrel in 2002 to provide digital ASIC designs.

How did you aim to differentiate Sondrel when you started?

My view of the market was that there were a lot of small design companies and also huge in-house design… Read More

Based on the Intel investor call yesterday here are some interesting comments Bob Swan made related to Intel outsourcing manufacturing and 7nm progress. Let’s start with the prepared statement:

Bob Swan: “Over the last couple of years, we have been focused on three critical priorities; improving our execution to strengthen … Read More

We all know the signal integrity and power integrity challenges of high-performance system design. It used to be enough to design a robust chip. Now, the interaction between the chip, the substrate/package and the PCB all matter. If your design is 2.5D, as many are these days, the problems just gets worse. Chiplets are becoming… Read More

Summary

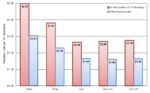

The growing significance of ultra-short reach (USR) interfaces on 2.5D packaging technology has led to a variety of electrical definitions and circuit implementations. TSMC recently presented the approach adopted by their IP development team, for a parallel-bus, clock-forwarded USR interface to optimize power/performance/area… Read More