You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

I have been at the Linley Microprocessor Conference today. This is the one that is not about mobile: about servers, networking, base-stations. Probably the most important story about the whole industry is that the “shift to ARM becomes a stampede.”

In this market it seems to be driven by the 64-bit ARMv8 instruction… Read More

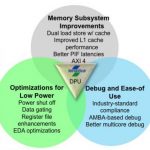

Chris Rowen of Cadence’s Tensilica announced the tenth generation of the Xtensa customizable processor at the Linley Microprocessor Conference yesterday. Chris was one of the founders of Tensilica…back in 1997. I believe that the first version was released in 1999. Over the years the Tensilica business changed.… Read More

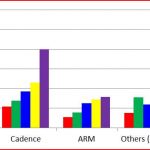

The GSA IP Working Group will meet today in San Jose, and the Group has asked IPnest building a presentation dedicated to Interface IP. The timing was perfect, as I have just completed the “Interface IP Survey” version 5, and I was able to use fresh market data. The IP working group will discover the IP vendor ranking, protocol by protocol,… Read More

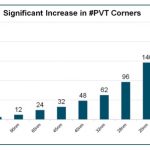

Transistor-level circuit designers have an insatiable appetite to run numerous SPICE circuit simulations in order to determine circuit speed, current and power across Process, Voltage and Temperature (PVT) conditions. Just look at the number of PVT corners increasing as the technology nodes go to 16nm:

The good news today … Read More

There is an interesting discussion on SemiWiki in regards to the age old question aboutbenchmarking EDA tools. I remember benchmark discussions at my first DAC in 1984. It was deemed impossible to do a “fair” public benchmark then and it’s not possible now, just my opinion of course but let me tell you why. Simply stated it is a legal,… Read More

At this year’s DAC, I spoke with several friends at Cadence. I got the distinct impression that something at Cadence had changed. There was a sense of pride and accomplishment that it seems to me had drifted away over the years. Now employees were speaking with true conviction about the accomplishments of the product development… Read More

From chip IP vendor ARM Holdings to semiconductor foundry Taiwan Semiconductor, there have been many winners from the mobile device revolution that was sparked by Apple’s introduction of the iPhone. However, while these big-ticket names get all the fame and glory, the electronic design automation space (“EDA” for short) is … Read More

VIPs (Verification IPs) are really important in this complex world of SoCs which involve various IPs, interfaces and continuously evolving protocols and standards, thus making the task of verifying an overall system extremely challenging. And the verification must be done in minimum possible run-time and memory consumption.… Read More

Analog and mixed-signal ICs are tougher to design and verify compared to digital, so if you want to learn more about best practices from actual AMS engineers then consider attending a summitthat is sponsored by Cadence Design Systems next Thursday, October 10th in San Jose from 8:00AM until 6:30PM.

They’ve lined up an interesting… Read More

As a blogger in the EDA industry I get to write every week, however I also end up reading every blog on SemiWiki plus multiple other sites to keep current on what’s happening in our business. I thought that it would be informative to look at Cadence Design Systems and how they are using blogging to talk not just about their own EDA… Read More