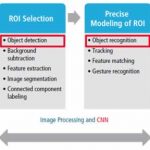

Every day I read stuff about the coming of fully autonomous vehicles, and it’s not every day we get a technologist’s view of the hurdles faced in getting there. Chris Rowen, CTO of Cadence’s IP group, gave one of the best presentations I’ve seen on ADAS technology and convolutional neural networks (CNNs) at #53DAC, pointing… Read More

Tag: cadence

IC Designers talk about 28nm to 7nm challenges at #53DAC

IC design challenges are different at advanced nodes like 7nm, so to learn more about the topic I attended a panel luncheon at DAC sponsored by Cadence. The moderator was both funny and technically astute, quite the rare combination, so kudos to Professor Rob Rutenbar, a former Neolinear guy now at the University of Illinois. Panelists… Read More

ARM sets up quagmire-free ecosystem for IoT

Wandering around DAC this week, I found much of the discussion focused on the EDA community being at an inflection point. How do we get more design starts from new places with new ideas without jeopardizing existing business? It’s not as simple a transition as it sounds.… Read More

Reusable HW/SW Interface for Portable Stimulus

Although semiconductor community has ushered into the era of SoCs, the verification of SoCs is still broken. There is no single methodology or engine to verify a complete SoC; this results in duplication of efforts and resources for test creation and verification at multiple stages in the SoC development, albeit with different… Read More

Quick Guide to FD-SOI at #53DAC

If you’re headed to #53DAC (June 5-9 in Austin,TX) and are interested in learning more about FD-SOI, there will be lots of opportunities. Here’s a quick guide to get you started. … Read More

Six Reasons to Visit Cadence at #53DAC this Year in Austin

For bloggers like myself spending four days at #53DAC is almost a non-stop blur of activity, visiting EDA vendors, IP providers and foundries to learn about what’s happening in our semiconductor industry. Cadence is both an EDA vendor and IP provider, so DAC is a great showcase for them to tell us what’s new in 2016 and… Read More

Body-biasing for ARM big or LITTLE in GF 22FDX

GLOBALFOUNDRIES has been evangelizing their 22FDX FD-SOI process for a few months; readers may have seen Tom Simon’s write-up of their preview at ARM TechCon. Dr. Joerg Winkler recently gave an updated webinar presentation of their approach in an implementation of ARM Cortex-A17 core.

By now, you’ve probably heard that 22FDX… Read More

Eight Improvements for PCB Software

I first met John Durbetaki at Intel in Aloha, Oregon and we both had a keen interest in the nascent personal computer industry. My first PC was made by Radio Shack and dubbed the TRS-80 which maxed out at 48KB of RAM. I kept watch on Durbetaki as he left Intel and formed his own company OrCAD in 1985 to serve the needs of PC-based CAD software.… Read More

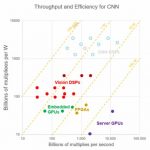

Cadence loads up on MACs for vision with CNNs

For vision DSP IP running convolutional neural networks (CNNs), a big driver of performance is increasing the bits processed per cycle with parallel MACs. Tom Simon did a great job in recent posts of introducing CNNs at a high level, so I’ll look at what is architecturally behind Cadence’s latest announcement: the Tensilica Vision… Read More

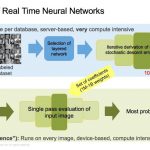

Neural Networks Poised to Make Big Changes in Our World

Probably the most interesting thing about Neural Networks is how they can be used for complex recognition tasks that we as people can easily perform but we might have a lot of trouble explaining how. One very good example of a problem that Neural Networks can tackle is determining when people are making a fake smile. Intuitively we… Read More