I’ve been hearing about the Portable Stimulus Standard (PSS) since DAC 2016, so it’s helpful to get an update from EDA vendors on what their involvement level is with this emerging standard and how they see it helping design and verification engineers. Earlier in September I scheduled a conference call with Cadence… Read More

Tag: cadence

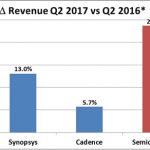

Semiconductor and EDA 2017 Update!

It really is an exciting time in semiconductors. The benchmarks on the new Apple A11 SoC and the Nvidia GPU are simply amazing. Even though Moore’s Law is slowing, the resulting chips are improving well above and beyond expectations, absolutely.

As I have mentioned before, non-traditional chip companies such as Apple, Amazon,… Read More

Improved Memory Design, Characterization and Verification

My IC design career started out with DRAM design, characterization and verification back in the 1970’s, so I vividly recall how much SPICE circuit simulation was involved, and how little automation we had back in the day, so we tended to cobble together our own scripts to help automate the process a bit. With each new process… Read More

TSMC OIP Ecosystem Forum 2017 Preview!

The TSMC OIP Ecosystem Forum is upon us again. I have yet to meet a disappointed attendee so it is definitely worth your time: Networking with more than 1,000 semiconductor professionals, the food, mingling with the 50+ EDA, IP, and Services Companies, the food, and of course the content. The 7nm and 7nm EUV updates alone are worth… Read More

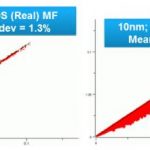

Extraction Features for 7nm

Frequent Semiwiki readers are familiar with the importance of close collaboration between the foundries and EDA tool developers, to provide the crucial features required by new process nodes. Perhaps the best illustration of the significance of this collaboration is the technical evolution of layout parasitic extraction.… Read More

Overcoming Mixed-Signal Design and Verification Challenges in Automotive and IoT Systems

At the recent DAC conference in Austin I attended a panel discussion over lunch where engineers from four companies talked about how they approached mixed-signal design and verification challenges for automotive and IoT systems. It seems like 2017 was the year of automotive at DAC, while in 2016 it was all about IoT. Both segments… Read More

ADAS and Vision from Cadence

A huge theme at #54DAC this year was all things automotive and in particular the phrase ADAS (Assisted Driver Assistance Systems), so I followed up with Raja Tabet a corporate VP of emerging technology at Cadence. We met on Monday in a press room where I quickly learned that Cadence has been serving the automotive industry for the … Read More

Cadence Design Systems @ #54DAC!

This year Cadence Design Systems is showcasing system design enablement in their booth, capitalizing on the industry shift from naked chip design to system level chip design. Apple started it with making the chips inside the iProducts as part of the system and now other systems companies are looking to take more control over their… Read More

FD-SOI in Japan?

If you want to get your finger on the Japan FD-SOI pulse, registration is still open for a free, two-day workshop in Tokyo this week organized by the SOI Consortium. This is the 3rd Annual SOI Tokyo Workshop, and there’s a really interesting line-up of speakers.

In case you’re wondering, Japan is doing FD-SOI. In fact… Read More

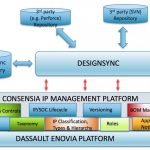

Webinar: Next Generation Design Data & Release Management

Design Data Management (DDM) is a bit like insurance. It’s something every semiconductor company has to have, and as a result it’s probably something taken for granted. In order to make their products more useful, the DDM vendors have added more functionality to manage more of the lifecycle of design data.

Dassault’s Synchronicity… Read More