It is microprocessors all the time right now, with Linley last week. Today ARM announced the next generation Cortex-A17 core. It is a development built on the Cortex-A12 core, itself built on A7 (which is the current volume leader). ARM says that it is 60% faster than the A7 core, although I’m sure a lot of that gain is a process… Read More

Tag: arm

A Brief History of Qualcomm

Qualcomm is the largest fabless semiconductor company in the world. If you have a smarphone there is a good chance you have a Qualcomm chip in your pocket. It is headquartered in San Diego with offices pretty much everywhere.

Qualcomm’s roots are in Linkabit, which was founded by Irwin Jacobs and Andrew Viterbi. They, along with … Read More

The Semiconductor Landscape – III

In continuation to my earlier observations and anticipations (landscape1, landscape2) which came up to my expectations, I was further inspired to ponder over the macros of our ever growing semiconductor industry. We may argue the business is stagnating, we may argue that the pace of scaling is slowing, but when I look back at the… Read More

SilabTech Awarded 2013 Best Start-up in India

This is obviously great news for SilabTech, and this is the type of news which will change the perception that we (non-Indian) have of the Semiconductor industry in India. About 15-20 years ago, the India Embedded/VLSI industry was perceived as low cost design resource pool, a good place where to implement design center. The hidden… Read More

Intel is NOT Transparent Again!

Recent headlines suggest that Intel was not transparent about some of the products they showed at the CES keynote. Intel confirmed on Friday that they used ARM-based chips for some of the products but would not say which ones. When your company’s tag line is “Intel Inside” and you hold up a product during your keynote wouldn’t… Read More

How to Develop Accurate Yet High Performance Models

In today’s environment of semiconductor design, SoCs are crammed with various IPs with multiple functionalities and processors integrated together. In such an event it has become necessary to model the system and verify on Virtual Platform before getting into actual design and fabrication. And that requires modelling of each… Read More

A Brief History of Andes Technology

I like to call Andes Technology the biggest microprocessor IP company you’ve never heard of. I wrote about themback in October when I sat down with them during the Linley Microprocessor Conference. Part of the reason you have never heard of them is that they are based in Taiwan and most of their business is in Taiwan and China.… Read More

Taming The Interconnect In Real World For SoCs

Interconnect plays a significant role in the semiconductor design of a SoC; if not architected and handled well, it can lead to an overdesigned SoC impacting on its power, performance and area. Since a SoC generally contains multiple IPs requiring different data paths to satisfy varying latency and performance cycles, it has … Read More

A Brief History of ARM Holdings

It was on 26th April 1985 (at 3pm to be precise) that the very first ARM silicon sprang in to life – it was a 25K transistor design implemented in 3um technology with just 2 layers of metal.

However back then the “A” in ARM stood for Acorn – ARM the company had yet to be formed. Acorn sold computers to schools and so cost… Read More

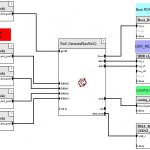

Cadence & ARM Optimize Complex SoC Performance

Now a day, a SoC can be highly complex, having 100s of IPs performing various functionalities along with multi-core CPUs on it. Managing power, performance and area of the overall semiconductor design in the SoC becomes an extremely challenging task. Even if the IPs and various design blocks are highly optimized within themselves,… Read More