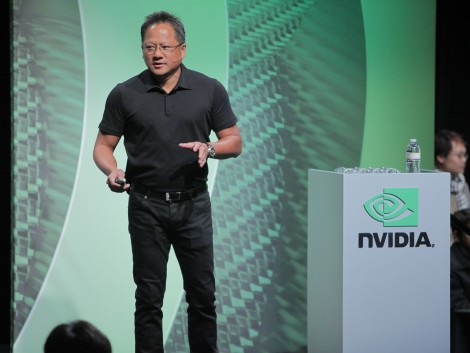

Jen Hsun Huang, the CEO of nVidia, has a phrase he often repeats to his employees: “We are 30 days from going out of business.” With product cycles as short as 6 months, the troops are on a constant march to revenue. The earnings conference call on August 11th highlighted two critical pieces of information. First, is the success that… Read More

Tag: arm

Smartphones shipments, Sky is the limit…

…or a global recession, but that’s not the purpose of this blog. As everybody knows, Apple is designing and selling smartphones, only. Does it mean that only smartphones are generating profit in the mobile industry? As we have seen recently in Semiwiki, Apple makes 2/3 of profit of entire mobile industry.

Let’s have a look (below)… Read More

MCU Performance Customers: The Cavalry is Coming Over The Hill

The under the radar, sleepy microcontroller market is about to undergo a rapid transformation the next several years with new entrants and the rise of 32 bit cores that will redefine the parameters for success. This will revive growth and result in new winners and losers. But lots of questions remain.

My first job out of college in… Read More

Cache Coherency and Verification Seminar

At DAC Jasper presented a seminar with ARM on cache coherency and verification of cache coherency. The seminar is now available online for those of you that missed DAC or missed the seminar itself.

Cache architectures, especially for multi-core architectures, are getting more and more complex. Techniques originally pioneered… Read More

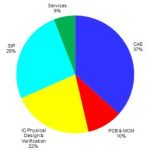

Silicon IP to take over CAE in EDAC results… soon but not yet!

Very interesting results launched by EDAC for Q1 2011, if Computer Aided Engineering (CAE) is still the largest category with $530.6M, the second category is Silicon IP (SIP) with $371.4M, followed by IC Physical Design & Verification at $318.5M. Even more significant is the four quarter moving average results, showing … Read More

And it’s Intel at 22nm but wait, Samsung slips ahead by 2nm…

Another announcement of interest, given all the discussion of Intel’s 22nm process around here, is that Samsung (along with ARM, Cadence and Synopsys) announced that they have taped out a 20nm ARM test-chip (using a Synopsys/Cadence flow).

An interesting wrinkle is that at 32nm and 28nm they used a gate-first process but… Read More

On-chip supercomputers, AMBA 4, Coore’s law

At DAC I talked with Mike Dimelow of ARM about the latest upcoming revision to the AMBA bus standards, AMBA 4. The standard gets an upgrade about every 5 years. The original ARM in 1992 ran at 10MIPS with a 20MHz clock. The first AMBA bus was a standard way to link the processor to memories (through the ARM system bus ASB) and to peripherals… Read More

Intel Twisting ARM?

Intel’s new Tri-Gate technology is causing quite a stir on the stock chat groups. Some have even said if Intel uses its Tri-Gate technology on only Intel processors ARM will be in deep deep trouble. These guys are “Intel Longs” of course and they are battling “Intel Shorts” with cut and paste news clips.

“ARM is in trouble & this… Read More

ARM and Mentor Team Up on Test

Introduction

Before DAC I met with Stephen Pateras, Ph.D. at Mentor Graphics, he is the Product Marketing Director in the Silicon Test Solutions group. Stephen has been at Mentor for two years and was part of the LogicVision acquisition. He was in early at LogicVision and went through their IPO, before that he was at IBM in the mainframe… Read More

Synopsys, ARM, Samsung, GLOBALFOUNDRIES (Part 1 of 2)

Intro

The 28nm nodes is ready with foundry silicon, IP and EDA tools. Tuesday morning at the DAC breakfast I learned more about the 28nm eco-system.

Notes

Why 32/28nm

–Lower power, high integration requirements, mobile applications

What is Ready?

–IP is qualified (ARM, Memories, Foundation IP, SNPS IP, PDKs)

–… Read More