The explosion in volume and consumption of data, fueled by industry trends in virtualization, networking, and computing among others, continues to push photonic solutions forward into leading positions. On Feb 2nd, I attended a panel by Ansys at DesignCon that brought together industry experts from Intel, GlobalFoundries,… Read More

Tag: ansys

CES 2023 and all things cycling

It’s January so time for me to review what I’ve found at CES this year that relates to cycling. Unlike last year when there were many last-minute cancellations from exhibitors, in 2023 it’s in-person and bigger than ever. The electrification of bikes continues, and many of these electronic devices are cloud… Read More

Whatever Happened to the Big 5G Airport Controversy? Plus A Look To The Future

In December 2021, just weeks before Verizon and AT&T were set to enable their new radio access networks in the 5G mid-band spectrum (also known as C-Band), the Federal Aviation Administration (FAA) released a Special Airworthiness Information Bulletin (SAIB) and a statement notifying operators of potential 5G interference… Read More

What Quantum Means for Electronic Design Automation

In 1982, Richard Feynman, a theoretical physicist and Nobel Prize winner, proposed the initial quantum computer; Feynman’s quantum computer would have the capacity to facilitate traditional algorithms and quantum circuits with the goal of simulating quantum behavior as it would have occurred in nature. The systems Feynman… Read More

The Lines Are Blurring Between System and Silicon. You’re Not Ready.

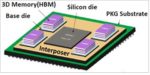

3D-ICs bring together multiple silicon dies into a single package that’s significantly larger and complex than traditional systems on a chip (SoCs). There’s no doubt these innovative designs are revolutionizing the semiconductor industry.

3D-ICs offer a variety of performance advantages over traditional SoCs. Because … Read More

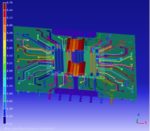

Multiphysics, Multivariate Analysis: An Imperative for Today’s 3D-IC Designs

Semiconductor manufacturers are under constantly increasing and intense pressure to accelerate innovative new chip designs to market faster than ever in smaller package sizes while assuring signal integrity and reducing power consumption. Three-dimensional integrated circuits (3D-ICs) promise to answer all these demands… Read More

A Different Perspective: Ansys’ View on the Central Issues Driving EDA Today

For the past few decades, System-on-Chip (SoC) has been the gold standard for optimizing the performance and cost of electronic systems. Pulling together practically all of a smartphone’s digital and analog capabilities into a monolithic chip, the mobile application processor serves as a near-perfect example of an SoC. But… Read More

Take a Leap of Certainty at DAC 2022

The live events I have attended thus far this year have been very good. As much as I liked the virtual events, attending in the comfort of my home or sailboat, it is great to be live and networking inside the semiconductor ecosystem, absolutely.

Ansys has been a great supporter of the Design Automation Conference but this year they … Read More

Bespoke Silicon is Coming, Absolutely!

It was nice to be at a live conference again. DesignCon was held at the Santa Clara Convention Center, my favorite location, which to me there was a back to normal crowd. The sessions I attended were full and the show floor was busy. Masks and vaccinations were not required, maybe that was it. Or there was a pent-up demand to get back engaged… Read More

Podcast EP68: The Foundation of Computational Electromagnetics

Dan is joined by Dr. Matthew Commens, product manager Ansys. Matt discusses an upcoming webinar series on the inner workings and capabilities of Ansys simulation software. How the series began, the impact and benefits and a view of the future are all covered.

Webinar Series: Learn the Foundation of Computational Electromagnetics… Read More