An incredibly pervasive trend at last year’s ARM TechCon was the IoT, and I expect this year to bring even more of the same, but with a twist. Where last year was mostly focused on ultra-low power edge devices and the mbed ecosystem, this year is likely to show a better balance of ideas across all three IoT tiers. I also expect a slew of … Read More

Tag: aldec

Case study illustrates 171x speed up using SCE-MI

As SoC design size and complexity increases, simulation alone falls farther and farther behind, even with massive cloud farms of compute resources. Hardware acceleration of simulation is becoming a must-have for many teams, but means more than just providing emulation… Read More

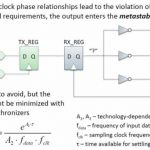

Up front phases improve CDC analysis

Many tools find clock domain crossings (CDCs) in FPGA designs. Some don’t find the right ones since they don’t comprehend things like in-house synchronizer constructs. Some find too many based on misunderstanding intent, inaccurate constraints, and other factors that lead to noise.… Read More

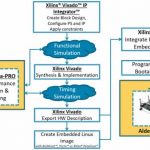

Optimization and verification wins in IoT designs

Designers tend to put tons of energy into pre-silicon verification of SoCs, with millions of dollars on the line if a piece of silicon fails due to a design flaw. Are programmable logic designers, particularly those working with an SoC such as the Xilinx Zynq, flirting with danger by not putting enough effort into verification?… Read More

Webinar alert – VHDL guru says its time to move up

Many years ago when I worked for Ed Staiano at Motorola, I learned never to use the word “comfortable” in a career context. I’m comfortable being with family and friends. This new high-back chair I sit in at my new faux-cocobolo desk (slightly distressed chalk-painted wood and industrial piping, awesome) is comfortable,… Read More

Webinar alert – Taking UVM to the FPGA bank

UVM has become a preferred environment for functional verification. Fundamentally, it is a host based software simulation. Is there a way to capture the benefits of UVM with hardware acceleration on an FPGA-based prototyping system? In an upcoming webinar, Doulos CTO John Aynsley answers this with a resounding yes.… Read More

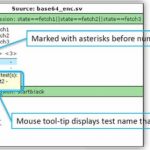

Design units come to faster Riviera-PRO release

For the latest incremental improvements to its Riviera-PRO functional verification platform, Aldec has turned to streamlining random constraint performance. The new Riviera-PRO 2016.02 release also is now fully supported on Windows 10 and adds a new debugger tool.… Read More

Aldec reprograms HES7 for AXI4 speed

FPGA-based prototyping firms are all grappling with the problem of higher speed connectivity between a development host and their hardware. Aldec is announcing their solution at DVCon 2016, turning to an AMBA AXI4 interface bridged into a host with PCIe x8.

Faster host interfaces deliver dual benefits in FPGA-based prototyping.… Read More

Updated tool cuts through DO-254 V&V chaos

Audits. The mere mention of the word keeps project managers up at night and sends most designers running. However, in the case of FPGA designs seeking DO-254 compliance, the product doesn’t ship until the audit is complete – there is no avoiding it, or skating around it.… Read More

Aldec updates two EDA product lines

Continuous, incremental improvement based on customer feedback and insight from researchers is a pillar of the Aldec EDA strategy. Within the last two weeks, two of the Aldec product lines – Riviera-PRO, and ALINT-PRO-CDC – have seen new version releases. Here’s a quick look at some of the highlights of both.

Riviera-PRO 2015.06… Read More