I previously wrote a blog about a session from Day 1 of the AI Hardware Summit at the Computer History Museum in Mountain View, CA, held just last week. From Day 2, I want to delve into this presentation by Bryan Bowyer, Director of Engineering, Digital Design & Implementation Solutions Division at Mentor, a Siemens Business.… Read More

Tag: ai/ml

eSilicon Brings a New Software Interface to its 7nm neuASIC Machine Learning Platform at Hot Chips

In early May of this year, eSilicon announced the tape-out of a test chip which included the latest additions to its neuASIC™ IP platform. At the upcoming Hot Chips Symposium to be held at Stanford on August 19 and 20, 2019, eSilicon will be demonstrating the software component of this AI-enabling IP platform. At the event, eSilicon… Read More

The Implications of the Rise of AI/ML in the Cloud

Recently, Daniel Nenni blogged on the presentation Wally Rhines gave at #56th DAC. Daniel provided a great summary, but I want to dive into a portion of the presentation in more detail. I love Wally’s presentations, but sometimes you cannot absorb the wealth of information he provides when you initially see it. It’s… Read More

Siemens Shows SOC Simulation Solution for Self-Driving Vehicles

Ever since the early days of computing there has always been a large distinction between ‘regular’ computing and real time computing – where special care had to be made to deal with unordered and asynchronous events. Back then a system typically consisted of a handful of sensors and perhaps some electromechanical devices.… Read More

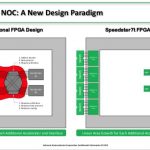

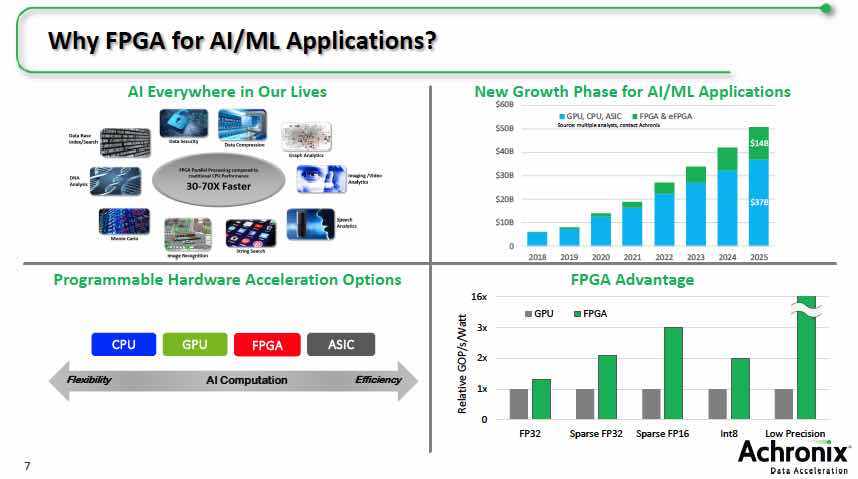

An evolution in FPGAs

Why does it seem like current FPGA devices work very much like the original telephone systems with exchanges where workers connected calls using cords and plugs? Achronix thinks it is now time to jettison Switch Blocks and adopt a new approach. Their motivation is to improve the suitability of FPGAs to machine learning applications,… Read More

Embeddable FPGA Fabric on TSMC 7nm

With their current line-up of embeddable and discrete FPGA products, Achronix has made a big impact on their markets. They started with their Speedster FPGA standard products, and then essentially created a brand-new market for embeddable FPGA IP cores. They have just announced a new generation of their Speedcore embeddable… Read More