Breker Verification Systems solves challenges across the functional verification process for large, complex semiconductors. This includes streamlining UVM-based testbenches for IP verification, synchronizing software and hardware tests for large system-on-chips (SoCs), and simplifying test sets for hardware emulation… Read More

Tag: accellera

MENTOR at DVCON 2019

The semiconductor conference season has started out strong and the premier verification gathering is coming up at the end of this month. SemiWiki bloggers, myself included, will be at the conference covering verification so you don’t have to. Verification is consuming more and more of the design cycle so I expect this event to … Read More

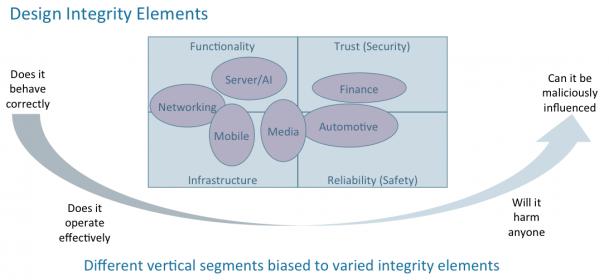

Design Integrity Investment Thesis Part 2

It is important when talking about a market to first establish the need and potential growth, then determine how the market is being served. This requires examining product features and services offered. … Read More

Portable Stimulus enables new design and verification methodologies

My usual practice when investing is to look at startup companies and try to understand if the market they are looking to serve has a significant opportunity for a new and disruptive technology. This piece compiles the ideas that I used to form an investment thesis in Portable Stimulus. Once collected, I often share ideas to get feedback.… Read More

Lu Dai: Incoming Accellera Chair

One of the fun things about what I do is getting to meet some of the movers and shakers in the industry. You might not think of Accellera as a spot to find movers and shakers, but when you consider the impact they have had on what we do (OVL, SystemVerilog, UVM, UPF, SystemC, IP-XACT and others), design today would be unrecognizable without… Read More

Reusable HW/SW Interface for Portable Stimulus

Although semiconductor community has ushered into the era of SoCs, the verification of SoCs is still broken. There is no single methodology or engine to verify a complete SoC; this results in duplication of efforts and resources for test creation and verification at multiple stages in the SoC development, albeit with different… Read More

SystemC and Adam’s Law

At DVCon I sat in on a series of talks on using higher-level abstraction for design, then met Adam Sherer to get his perspective on progress in bringing SystemC to the masses (Adam runs simulation-based verification products at Cadence and organized the earlier session). I have to admit I have been a SystemC skeptic (pace Gary Smith)… Read More

Accellera and Portable Stimulus

I’ll start with a quick note on DVCon. This seems to be gaining momentum each year. In addition to the events in the US, Europe and India, a DVCon event is now planned for China, kicking off in Shanghai in 2017. At a time when we’re all bemoaning the future of EDA and EDA conferences, DVCon is booming internationally, no doubt reflecting… Read More

HW/SW Interfaces for Portable Stimulus

With growing size and complexity of SoC, the semiconductor community is realizing the growing pain of verification. The cost of SoC verification grows exponentially with design size. Moreover, there is no single methodology for verifying a SoC; multiple engines are used in different contexts through different verification… Read More

Leveraging HLS/HLV Flow for ASIC Design Productivity

Imagine how semiconductor design sizes leapt higher with automation in digital design, which started from standard hardware languages like Verilog and VHDL; analog design automation is still catching up. However, it was not without a significant effort put in moving designers from entering schematics to writing RTL, which… Read More