Portable Stimulus has become such a popular standards topic of late that I thought it would be good to take a break this month from my low power series to bring you, my valued readers, more information about it from one of my colleagues, Dennis Brophy, who is working to help drive development of this standard within Accellera. I’ll … Read More

Tag: accellera

Nine Cost Considerations to Keep IP Relevant –Part2

In the first part of this article I wrote about four types of costs which must be considered when an IP goes through design differentiation, customization, characterization, and selection and evaluation for acquisition. In this part of the article, I will discuss about the other five types of costs which must be considered to enhance… Read More

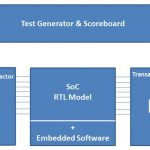

Moving up Verification to Scenario Driven Methodology

Verification complexity and volume has always been on the rise, taking significant amount of time, human, and compute resources. There are multiple techniques such as simulation, emulation, FPGA prototyping, formal verification, post-silicon testing, and so on which gain prominence in different situations and at different… Read More

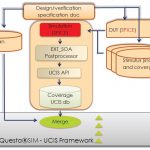

UVM Debugging Made Easy & Productive in Questa

As design complexity and size is increasing, SoC verification has become one of the most difficult and time consuming tasks in the design closure.UVM (Universal Verification Methodology, an accellera initiative) is one of the best verification methodologies that support common language, coherent strategy, clarity and transparency… Read More

Improving Verification by Combining Emulation with ABV

Chip deadlines and the time to achieve sufficient verification coverage run continuously in a tight loop like a dog chasing its tail. Naturally it is exciting when innovative technologies can be combined so that verification can gain an advantage. Software based design simulators have been the mainstay of verification methodologies.… Read More

Coverage Driven Verification for Analog?

We know there is a big divide between analog and digital design methodologies, level of automation, validation and verification processes, yet they cannot stay without each other because any complete system on a chip (SoC) demands them to be together. And therefore, there are different methodologies on the floor to combine analog… Read More

Analog Model Equivalence Checking Accelerates SoC Verification

In the race to reduce verification time for ever growing sizes of SoCs, various techniques are being adopted at different levels in the design chain, functional verification being of utmost priority. In an analog-digital mixed design, which is the case with most of the SoCs, the Spice simulation of analog components is the limiting… Read More

With SCE-MI, timing really is everything

In one of my favorite movies, Brad Pitt utters the only question that matters in baseball or technology management in the face of uncertainty: “Okay, good. What’s the problem?” Not surprisingly in that scene, as the question circles the table of experts used to doing things the old way, not a single one can answer it correctly in the… Read More

UVM/SystemVerilog: Verification and Debugging

At DAC in just three weeks you can learn about which EDA vendors are supporting the latest UVM 1.1d (Universal Verification Methodology) standard as defined by Accellera. One of those EDA vendors is Aldec, and they have a 45 minute technical session that you can register for online. Space will fill up quickly, so get signed up sooner… Read More

ISCUG – Excellent Indian Conference, needs to grow

Promoted by Accellera, SystemC User Groups are in work worldwide; NASCUGin North America, ESCUGin Europe and ISCUG in India. While I was shuffling between my day-to-day work and strategy management course/exams, I received an invitation from my long time colleague, President and CEO of Circuitsutra Technologies, Mr. Umesh… Read More