The Accellera organization created the concept of a Unified Power Format (UPF) back in 2006, and by 2007 they shared version 1.0 so that chip designers would have a standard way to communicate the power intentions of IP blocks and full chips. By 2009 the IEEE received the Accellera donation on UPF , reviewed multiple drafts and published… Read More

Tag: accellera

Accellera at DVCon U.S. 2022 in the Metaverse!

The premier verification conference and exhibition is coming up and of course Accellera plays an important role. This year DVCON will again be virtual, which is unfortunate, but I must say as a long time attendee this year’s program really stands out. In fact, there is a new addition that is worth mentioning, it’s the… Read More

What’s New with UVM and UVM Checking?

About once a quarter, I touch base with Cristian Amitroaie, CEO and co-founder of AMIQ EDA, to see what’s new with the company, products, and users. Sometimes he surprises me, as he did earlier this year when he mentioned that their tools check about 150 rules for non-standard constructs in SystemVerilog and VHDL. When we talked … Read More

Functional Safety – What and How

I’ve written before about how the automotive industry adheres to functional safety (FS) as defined in the ISO 26262 standard, along with other SemiWiki bloggers. That standard certainly defines the What part of FS, however it doesn’t mandate how you meet the standard, what tools you should be using, file formats … Read More

CEO Interview: R.K. Patil of Vayavya Labs

RK has over 25 years of industry experience in the domain of Telecom, Embedded software and Semiconductors. Before co-founding Vayavya, he was a co-founder at Smart Yantra Technologies, where he has held various positions in engineering, marketing and management. At Vayavya RK is responsible for overall management and strategic… Read More

CEO Interview: Dr. Chouki Aktouf of Defacto

“For more than 18 years, we never stopped innovating at Defacto. We are aware of EDA Mantra “Innovate or Die!”. Innovation is in our DNA, and we never stopped adding new automated capabilities to the SoC design community to help facing complexity and cost challenges, which increase every year.”

Before founding Defacto… Read More

Can you really meet your SoC design schedule without a good GUI?

Talk to the members of a digital design team and you will always find two types of users. One who likes using the GUI while working on his design and the other who is passionate about using scripts and the command line options. This is akin to the two camps of users who either love either good old Vi/Vim or the ever versatile Emacs editor.… Read More

Mentor at DVCON 2020!

Are you ready for the premier conference for functional design and verification of electronic systems?

Sponsored by Accellera Systems Initiative, DVCon is an independent, not-for-profit organization dedicated to creating design and verification standards required by systems, semiconductor, intellectual property (IP)… Read More

DVCon Is a Must Attend Event for Design and Verification Engineers

Learning is a never-ending process for design and verification engineers, so outside of reading SemiWiki you likely want to attend at least a few events per year to keep updated, learn something new, attend a workshop, or even present something that has made your IC project work much better than before. Sure, DAC is always a great… Read More

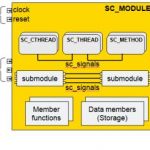

Update on SystemC for High-Level Synthesis

The scope of current system designs continues to present challenges to verification and implementation engineering teams. The algorithmic complexity of image/voice processing applications needs a high-level language description for efficient representation. The development and testing of embedded firmware routines… Read More