You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

On Tuesday, July 12th at SEMICON West I had an opportunity to sit down with Marie Semeria, the CEO of Leti and discuss the status and future of FDSOI. Leti pioneered FDSOI 15 years ago and has been the leading FDSOI research ever since.

Two years ago Leti and ST Micro demonstrated products on 28nm that are cost competitive with bulk technology.… Read More

The development of leading edge semiconductor technology is incredibly expensive, with estimates ranging from a few to several billion dollars for new nodes. The time to develop a leading edge process is also a critical competitive issue with some of the largest opportunities awarded based on who is first to yield on a new node.… Read More

IMEC is a technology research center located in Belgium that is one of the premier semiconductor research centers in the world today. The IMEC Technology Forum (ITF) is a two-day event attended by approximately 1,000 people to showcase the work done by IMEC and their partners.

Gary Patton is the Chief Technical Officer and Senior… Read More

Being that TSMC and Solido are founding members of SemiWiki, you should be able find out everything you ever wanted to know on their respective landing pages. If not, just ask a question in the SemiWiki forum and I can assure you it will be answered in great detail. And here are some other interesting 2015 factoids from Solido:… Read More

I have written multiple articles about this year’s SPIE Advanced Lithography Conference describing all of the progress EUV has made in the last year. Source power is improving, photoresists are getting faster, prototype pellicles are in testing, multiple sites around the world are exposing wafers by the thousands and more. … Read More

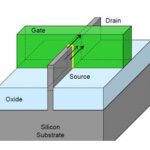

At ISSCC this year Samsung published a paper entitled “A 10nm FinFET 128Mb SRAM with Assist Adjustment System for Power, Performance, and Area Optimization. In the paper Samsung disclosed a high density 6T SRAM cell size of 0.040µm[SUP]2[/SUP]. I thought it would be interesting to take a look at how this cell size stacks … Read More

SPIE Days 3 and 4:

Anna Lio of Intel presented EUV resists: What’s next?

Intel wants to insert EUV at 7nm but it has to be ready and economical. Critical Dimension Uniformity (CDU), Line Width Roughness (LWR) and edge placement/stochastics are all stable on 22nm, 14nm and 10nm pilot lines.… Read More

About 35 years ago the first commercial SPICE circuit simulators emerged and they were quickly put to work helping circuit designers predict the timing and power of 6um NMOS designs. Then we had to limit our circuit simulations to just hundreds of transistors and interconnect elements to fit into the RAM and complete simulation… Read More

It used to be that GPU chips moved to new process nodes pretty frequently, previously as often as annually. That is up until 2011. That was the year that 28nm GPU’s were unveiled. Since then there has been a long pause. Now in the wake of the 2016 CES both Nvidia, with its previously announced Pascal, and AMD, with the just announced Polaris,… Read More

With every new technology node, there are newer physical effects that need to be taken into account. And every new physical effect brings with itself several new formats to model them. Often a format is also associated with several of its derivatives, sometimes an standard reincarnation of a proprietary format further evolved… Read More