Does this justify the widespread Intel bashing?

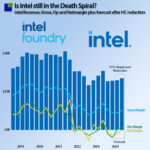

The latest Intel earnings release was another sharp and deeper turn into the company’s death spiral. On the surface, it is just a whole load of bad news, and the web has been vibrating with Intel bashing since the release.

So what are the facts?

From a revenue perspective, Intel was inside… Read More

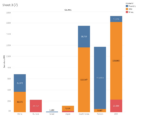

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!