FPGA-based prototyping offers advantages such as high-speed operation, real-world environment testing, and parallel execution that cannot be matched by software simulations alone. It enables developers to validate their designs and initiate software development long before the final silicon is ready. At the same time,… Read More

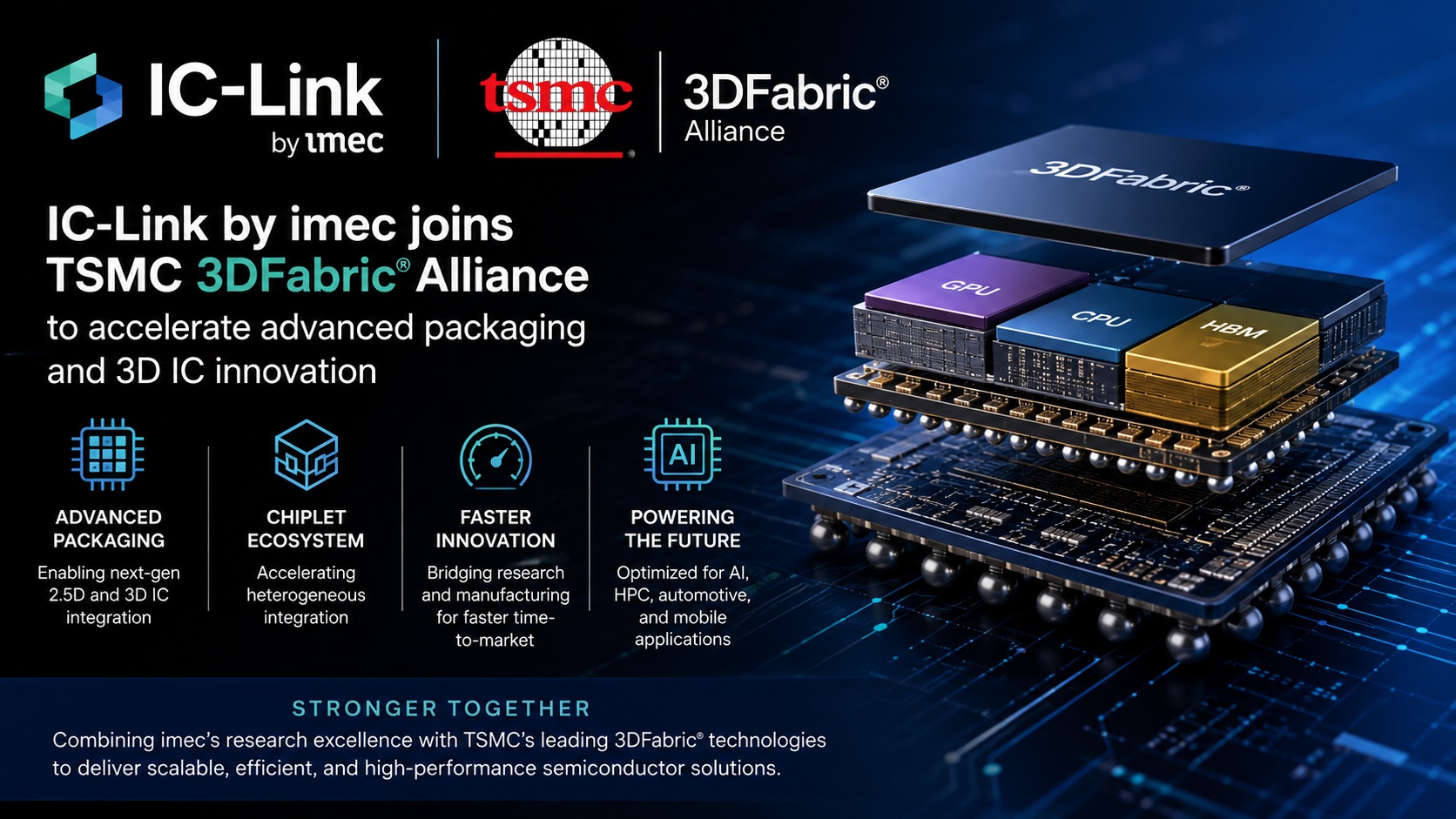

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scalingimec announced that IC-Link by imec has joined…Read More

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scalingimec announced that IC-Link by imec has joined…Read More From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read MoreMCUs Are Now Embracing Mainstream NoCs

The moral of today’s story is that to succeed in a late-adopter market, sometimes you just have to wait for the market to catch up (assuming you have a strong early adopter market to buy your product today). I have been working with Arteris for 6+ years now promoting their NoC technology, and there was never any question that they offer… Read More

CES 2025: All In on AI and Proposed Tariffs

CES 2025 was held last week in Las Vegas. We at Semiconductor Intelligence attended for our tenth CES. The event had over 140,000 attendees and over 4,500 exhibitors.

U.S. Consumer Electronics Market

Brian Comiskey of the Consumer Technology Association (CTA) presented on technology trends in 2025. The key theme was advances… Read More

Chiplet integration solutions from Keysight at Chiplet Summit

Chiplets continue gaining momentum, fueled in large part by applications for AI and 5G/6G RFICs. Keysight has a strong presence at this year’s Chiplet Summit in Santa Clara, which includes Simon Rance in a super panel discussing “Chiplets: The Key to Solving the AI Energy Gap” and Nilesh Kamdar with a keynote… Read More

A Deep Dive into SoC Performance Analysis: What, Why, and How

Part 1 of 2 – Essential Performance Metrics to Validate SoC Performance Analysis

Part 1 provides an overview of the key performance metrics across three foundational blocks of System-on-Chip (SoC) designs that are vital for success in the rapidly evolving semiconductor industry and presents a holistic approach to optimize… Read More

Advantest Wins Prestigious Excellent Performance Award at TSMC’s 2025 Supply Chain Management Forum

Advantest Corporation, a world-leading supplier of semiconductor test equipment, has been honored with the Excellent Performance Award at the 2025 Taiwan Semiconductor Manufacturing Company (TSMC) Supply Chain Management Forum. This recognition, presented by one of the semiconductor industry’s most influential companies,… Read More

2025 Outlook with Dr. Chouki Aktouf of Innova

Chouki Aktouf is Founder & CEO of Defacto Technologies and Co-Founder of Innova Advanced Technologies. Prior to founding Defacto in 2003, Dr. Aktouf was an associate professor of Computer Science at the University of Grenoble – France and leader of a dependability research group. He holds a PhD in Electric Engineering from… Read More

WEBINAR: Reconcile Design Cost Reduction & Eco-design Criteria for Complex Chip Design Projects

As chip design complexity keeps increasing, the challenge of managing costs becomes a pressing concern for companies of all sizes. Efficient resource management is emerging as a critical lever for controlling design expenses and ensuring project success.

The chip design market increasingly demands automated solutions for… Read More

Averting Hacks of PCIe® Transport using CMA/SPDM and Advanced Cryptographic Techniques

In today’s digital landscape, data security has become an indispensable feature for any data transfer protocol, including Peripheral Component Interconnect Express (PCIe). With the rising frequency and sophistication of digital attacks, ensuring data integrity, confidentiality, and authenticity during PCIe transport… Read More

2025 Outlook with Mahesh Tirupattur of Analog Bits

Tell us a little bit about yourself and your company.

I’m Mahesh Tirupattur. I’ve been with the company for over 20 years. Recently I took the role of CEO, where I drive business partnerships, IP licensing, and joint venture development. This change was a mutual decision between Alan Rogers and I. Alan wants to focus on technology… Read More

Crossing the Yield Cliff: IDP V6 and the Future of Manufacturing Forecasting