The Common Platform Alliance — IBM, Samsung Electronics, Co., Ltd., and GLOBALFOUNDRIES — continues to redefine the landscape of the semiconductor industry with its groundbreaking collaboration. Join us at our 2013 Common Platform Technology Forumon Tuesday, February 5, 2013 at the Santa Clara Convention Center as we showcase… Read More

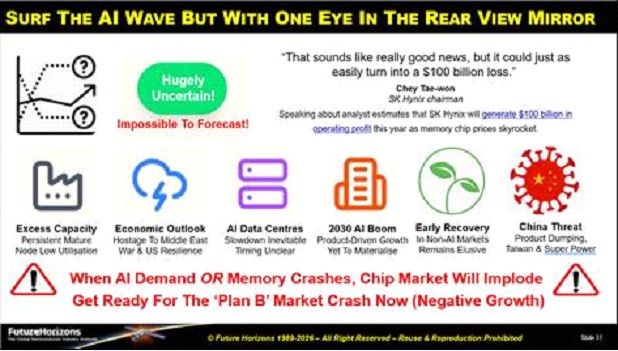

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

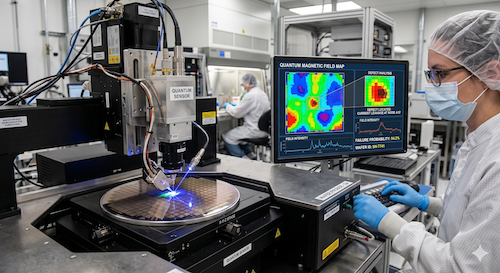

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read MoreAudio/Voice DSP IP core: the next road to billion unit shipment

When mentioning CEVA DSP IP cores, the first reaction is to think about the complexes DSP functions used into wireless Modem Application like 3G and Long Term Evolution (LTE). Considering that CEVA market share is above 70% for these products, such a reaction makes sense. But did you knew that CEVA DSP IP cores are also empowering… Read More

Engineer to Engineer, Embedded Instrumentation

Last month the folks at Tektronix did something very useful, they invited 30 engineers to talk directly with their chief engineer of embedded instrumentation as part of “Meet the Experts” in Santa Clara, CA.

Brad Quinton, Chief Architect created a new and efficient approach of embedding instrumentation in your … Read More

Apple’s Next Threat

It seems only appropriate that at the beginning of the year we should look at who is going to be the next significant threat to Apple’s profitability machine. During Apple’s meteoric rise over the past 9 years (APPL share price: Jan-2004 @ $11 vs. Jan-2013 @ $550) different companies have been put up as Apple’s next significant threat… Read More

Are you good at identifying languages? Win an iPad Mini

Did you watch Atrenta’s holiday video (it’s only one minute)? Various Atrenta employees from all over the world wished you happy holidays in their own languages. Now Atrenta are having a competition. If you identify all the languages in the video then you can win an iPad Mini.

To enter the competition, or to view the … Read More

HiFi Mini, Always Listening

Next week it is the Consumer Electronics Show (CES) in Las Vegas and so there are announcements around the areas where consumer overlaps with semiconductor, which these days is primarily mobile. Then in February in Barcelona is Mobile World Congress, which is even more focused on mobile. Expect more announcementst there.

Currently… Read More

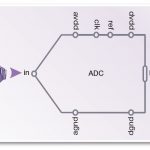

Integrating your SoC into the analog world

Our world is decidedly analog, made up of stimuli for our five basic senses of sight, touch, hearing, taste, and smell, and more advanced senses like balance and acceleration. To be effective on the Internet of Things, digital devices must integrate with the analog world, interfacing with sensors and control elements.… Read More

The Semiconductor Landscape – II

It has been a year since my article Semiconductor Landscape in Jan 2012 I wanted to look back into the major events over the year and then anticipate what’s in store going forward. What has happened over the year is much more than what I could foresee. Major consolidation in EDA space – Synopsys acquired Magma, SpringSoft, Ciranova,… Read More

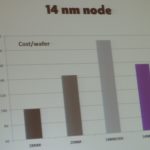

Wafer Costs: Out of Control or Not?

I didn’t attend the International Electronic Device Meeting (IEDM) earlier this month, but there have been a lot of reports on the inter webs especially about 20nm and 14nm processes. Some of this is really geeky stuff but I think that perhaps the most interesting thing I’ve read about is summarized in this chart:

This… Read More

Happy New Year from SemiWiki!

It was an amazing year for SemiWiki and I would like to sincerely thank all who participated. SemiWiki traffic doubled again which is amazing in itself. SemiWiki membership more than tripled as we continue to add vertical markets (EDA, IP, Services, Foundry). More people are blogging on SemiWiki and the Forums and Wikis are coming… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior