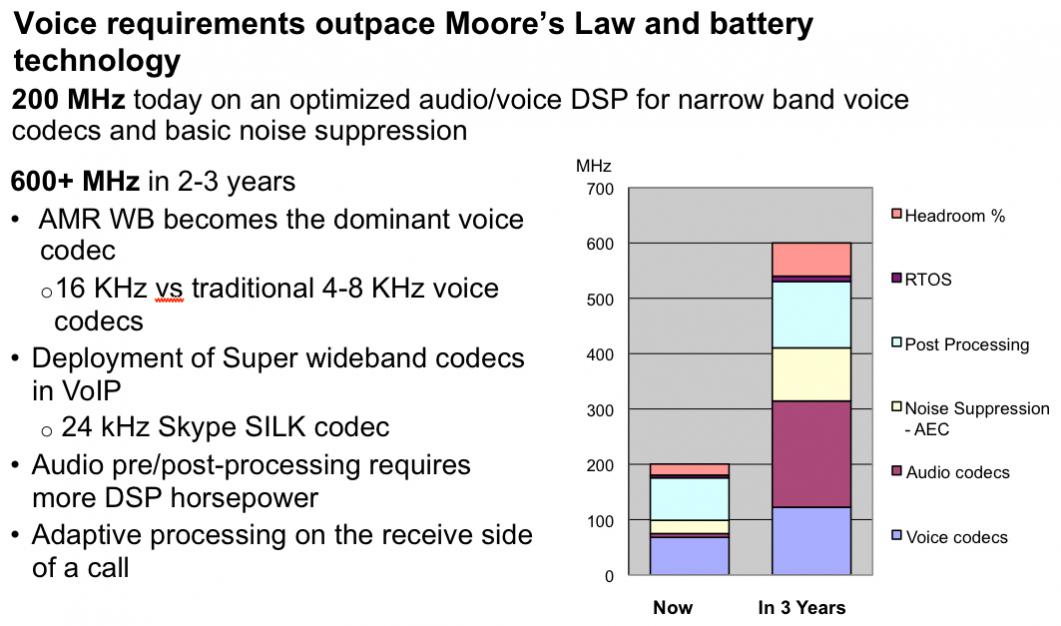

Chris Rowen, Tensilica’s CTO, presented in Santa Cruz at the Globalpress briefing. He was basically presenting Tensilica’s audio strategy, which I’ve written about before. But he provided an interesting perspective. Globalpress (which flies journalists in from all over the world and then fills the few… Read More

WEBINAR: Edge AI Optimization: How to Design Future-Proof Architectures for Next-Gen Intelligent DevicesEdge AI is rapidly transforming how intelligent solutions…Read More

WEBINAR: Edge AI Optimization: How to Design Future-Proof Architectures for Next-Gen Intelligent DevicesEdge AI is rapidly transforming how intelligent solutions…Read More WEBINAR Unpacking System Performance: Supercharge Your Systems with Lossless Compression IPsIn today's data-driven systems—from cloud storage and AI…Read More

WEBINAR Unpacking System Performance: Supercharge Your Systems with Lossless Compression IPsIn today's data-driven systems—from cloud storage and AI…Read More ChipAgents Tackles Debug. This is ImportantInnovation is never ending in verification, for performance,…Read More

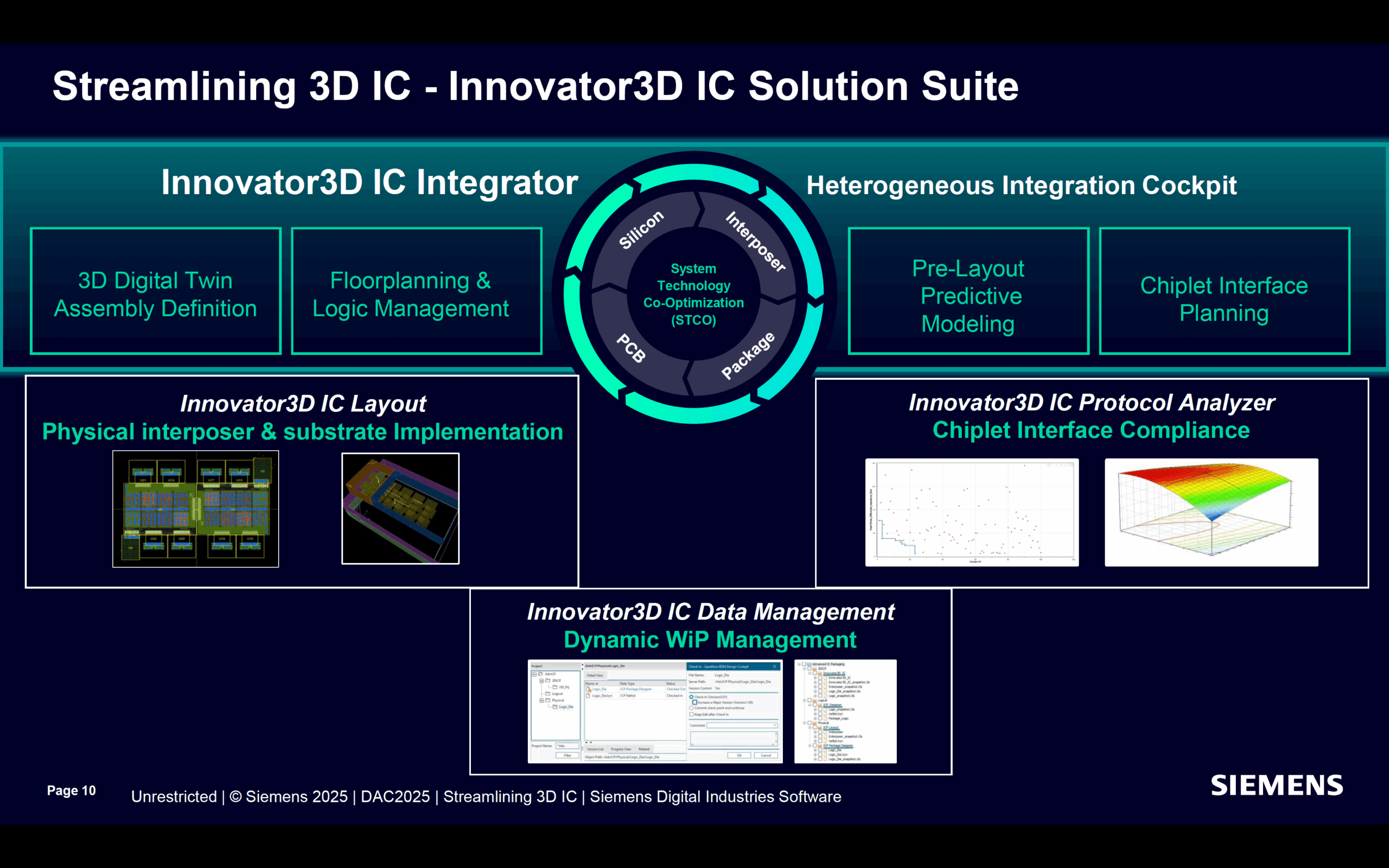

ChipAgents Tackles Debug. This is ImportantInnovation is never ending in verification, for performance,…Read More Siemens EDA Unveils Groundbreaking Tools to Simplify 3D IC Design and AnalysisIn a major announcement at the 2025 Design…Read More

Siemens EDA Unveils Groundbreaking Tools to Simplify 3D IC Design and AnalysisIn a major announcement at the 2025 Design…Read More CEO Interview with Faraj Aalaei of CognichipFaraj Aalaei is a successful visionary entrepreneur with…Read More

CEO Interview with Faraj Aalaei of CognichipFaraj Aalaei is a successful visionary entrepreneur with…Read MoreSmart mobile SoCs: Texas Instruments

TI has parlayed its heritage in digital signal processing and long-term relationships with mobile device makers into a leadership position in mobile SoCs. They boast a relatively huge portfolio of design wins thanks to being the launch platform for Android 4.0. On the horizon, the next generation OMAP 5 could change the entire… Read More

Broadcom announces an HFC

For a long time Cisco had a very high end product whose official internal name during its years of development was HFR, which stood for Huge F***ing Router (the marketing department insisted it stood for ‘fast’). Eventually it got given a product number, CRS-1, but not before I’d read an article about it in the… Read More

TSMC versus Intel at 20nm!

The biggest news out of the TSMC Symposium last week was the 20nm update. Lots of debate and speculation, just why is TSMC releasing one version of 20nm (20nm SoC) versus multiple versions like in 40nm (LP, G, LPG) and 28nm (HP, HPM, HPL, LP)? Here are my thoughts, I would also be interested in your feedback in the comment section. This… Read More

Mergers and Acquisitions in EDA should spark Innovation and Start ups

With the recent closure of the Synopsys Magma deal and the economy showing a bit of uptick and some positive outlook compared to the last 3-4 years, I believe it’s time for some of the creative minds that find themselves looking for new opportunity to consider starting their own point tool as well as IP companies.

Many of these people… Read More

DAC 2012 Must-See! Hogan’s Heros: Learning from Apple

Who doesn’t love the perennial Hogan’s Heros panel at DAC? Always provocative and illuminating, for technologists, entrepreneurs, and strategists.

At DAC 2012, Jim Hogan’s panel is “Learning from Apple”:Apple. We admire their devices, worship their creators and praisetheir stock in our portfolios. Apple is synonymous with… Read More

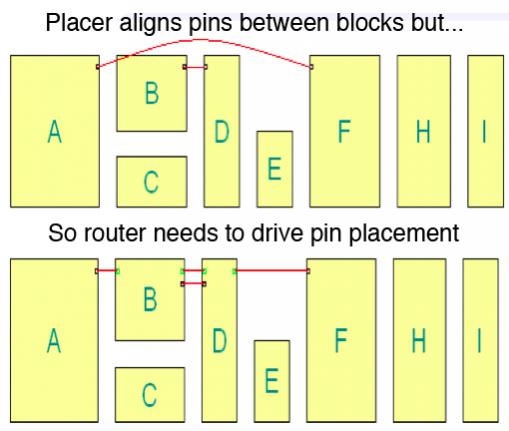

Channel Routing Memories

Back in the early days of ASIC when we had just two and then (wow!) three layers of metal, place and route was done by putting the standard cells in rows with gaps between them and then using a specialized router to do the interconnection. It would use one layer of metal horizontally and one vertically and avoid jogs. This was called a … Read More

AMS Design using Co-Simulation

The big three vendors in EDA offer AMS simulation tools but what about simulation choices from other EDA vendors?

It turns out there are two privately held EDA companies that have done business since the 1980’s and have just integrated a Verilog A simulator with a SPICE circuit simulator. The two companies are Aldec with a … Read More

UMC Wins Qualcomm 28nm Second Source Contract!

This is common knowledge in Taiwan but apparently the guys over at SemiAccurate.com did not get the memo. I hear a name change is in the works: www.RarelyAccurate.com. Remember, these are the same clairvoyants who said TSMC shut down 28nm which as we now know is absolutely false. The QCOM elite stay at the Hsinchu Royal Hotel which… Read More

Audio IP Subsystems Made Easy with a Complete, SoC-Ready Solution

After the launch of ARC based complete sound system IP by Synopsys last month, which could be the effective starting point for subsystem IP offering, providing the initiative will be successful (this was not really the case in the past, as we discussed it in our blog), the company proposes a webinar focusing on:

- The growing complexity

Facing the Quantum Nature of EUV Lithography