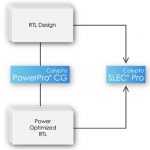

Sequential clock gating offers more power savings that can be obtained just with combinational clock gating. However, sequential clock gating is very complex as it involves temporal analysis over multiple clock cycles and examination of the stability, propagation, and observability of signal values.

Trying to do sequential… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!