EDA needs more CEOs like Amit Gupta. Solido, which is now profitable, is his second AMS EDA company. The first, Analog Design Automation (ADA), was purchased by Synopsys for a hefty multiplier. Prior to becoming an EDA entrepreneur, Amit was product manager for the wireless group at Nortel and a hardware engineer for the RF communications… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreCostello and Hogan Rock the House at Cadence EDAC ECC Event

No one who spent much time at Cadence during Joe Costello‘s reign as CEO (1987-1997, including SDA) could likely give an unbiased review of last night’s event, EDAC – Jim Hogan Emerging Companies Series. The event was held at Cadence’s 5-story Building 10, a building that had not yet been built while Joe… Read More

Multi-level abstraction accelerates verification turnaround

Often a question is raised about how SystemC improves verification time when the design has to go through RTL in any case. A simple answer is that with SystemC, designs can be described at a higher level of abstraction and then automatically synthesized to RTL. When the hands-on design and verification activity is at a higher level,… Read More

Kathryn Kranen Joins CriticalBlue’s Board

Jasper just announced that Kathryn Kranen, their CEO, had joined the board of CriticalBlue. I used it as an excuse to hit up CriticalBlue’s CEO Dave Stewart, who happened to be in the valley, for a free lunch to catch up on what they are doing.

CriticalBlue started about 10 years ago in Edinburgh (yay!). When it started it was in the business… Read More

An AMS Seminar on May 16th

Analog and Mixed-Signal (AMS) designers are facing more challenges than ever, so where can they go to get some relief? One place is a half-day seminar scheduled for May 16th in Bridgewater, New Jersey. SemiWiki has teamed up with Tanner EDA, Abbot Labs and SoftMEMS to present topics of:

- True collaborative design enabled through

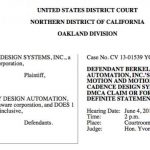

CDNS V. BDA: Motion to Dismiss

The Cadence-BDA saga continues with Berkeley Design Automation today filing a motion to dismiss. You can read the full motion HERE. My previous blog “Cadence Sues Berkeley Design Automation” with 30+ comments is HERE.

The first problem BDA brings up is that the DMCA claim by Cadence is so vague that it doesn’t… Read More

Costello on Story Telling

Last night at Cadence was the next installment of what I have been calling Hogan University. Jim interviewed Joe Costello about how to tell a story as part of the EDAC emerging companies series of events. The main focus was how to tell a story as a small EDA company communicating with investors, although there are obviously other forms… Read More

DAC: Calypto Insight Presentation

DAC has several “Insight Presentations” on Wednesday June 5th. Bryan Bowyer from Calypto will be presenting from 2-4pm that day (don’t know where, the DAC website doesn’t have a room number specified yet). The topic is Reducing Design and Debug Time with Synthesizable TLM. TLM, of course, stands for… Read More

DAC Keynotes: 5 This Year

DAC is in Austin this year, as I’m sure you know, and DAC has keynotes by CEOs of two Austin-based companies Freescale Semiconductor and National Instrument. Two more keynotes (one split into two) are focused on mobile, which has become the major driver of semiconductor today. A fifth keynote, including presentation of … Read More

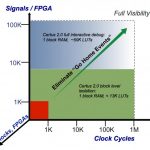

Accelerating Design Debug in an ASIC Prototype

ASIC prototyping in FPGAs is starting to trend on SemiWiki. As FPGA technology becomes more advanced customers tell me that the traditional debug tools are inadequate. Faced with the very restrictive debugging capabilities and very long synthesis/place/route times the debugging cycle in these prototype platforms are quite… Read More

Solving the EDA tool fragmentation crisis