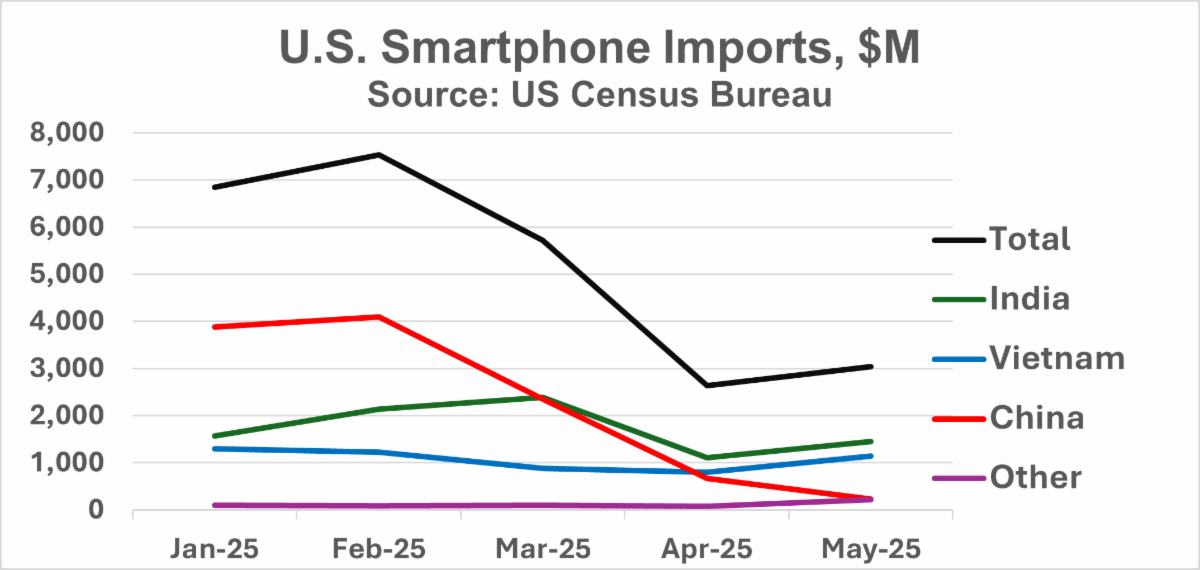

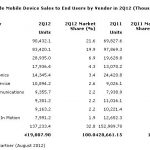

One of the comments to previous installments of this series was that there isn’t much left for the merchant suppliers of smart mobile SoCs, considering Apple and Samsung have majority share and design their own parts. The theory is this makes it hard for many suppliers to continue investing at the resource levels needed to bring … Read More

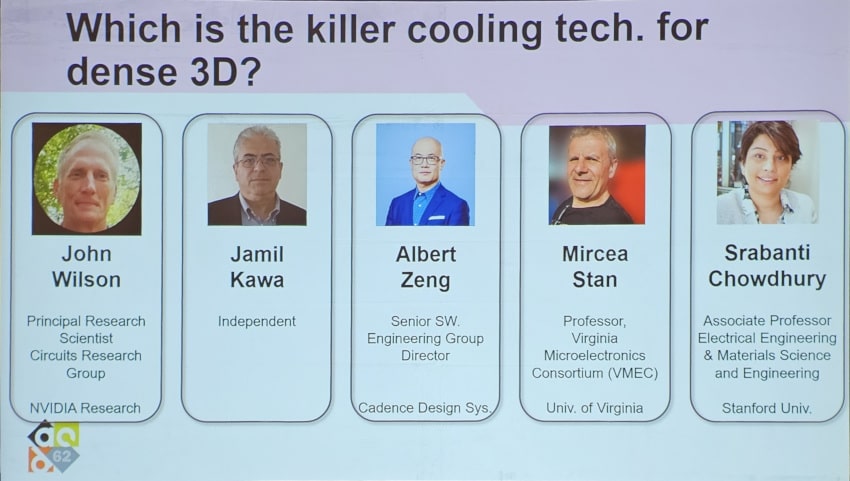

New Cooling Strategies for Future ComputingPower densities on chips increased from 50-100 W/cm2…Read More

New Cooling Strategies for Future ComputingPower densities on chips increased from 50-100 W/cm2…Read More DAC News – proteanTecs Unlocks AI Hardware Growth with Runtime MonitoringAs AI models grow exponentially, the infrastructure supporting…Read More

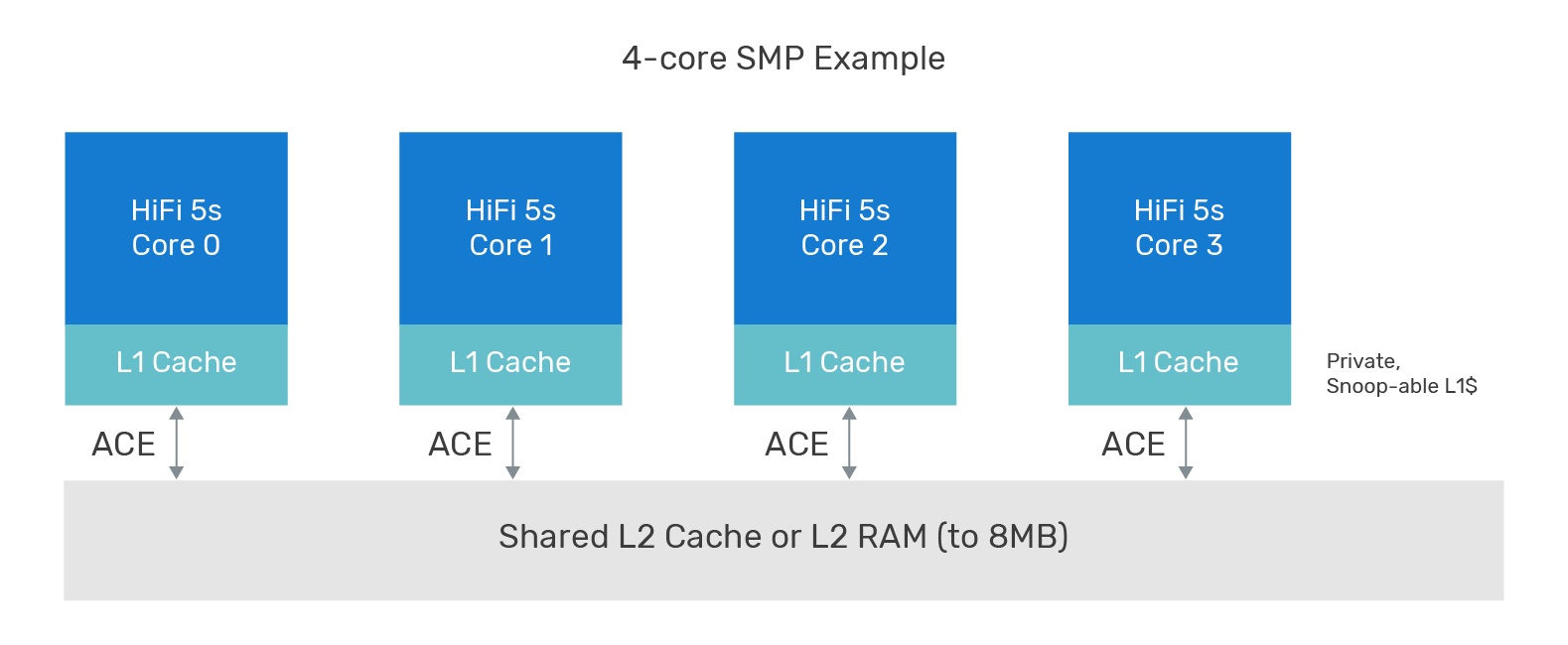

DAC News – proteanTecs Unlocks AI Hardware Growth with Runtime MonitoringAs AI models grow exponentially, the infrastructure supporting…Read More Sophisticated soundscapes usher in cache-coherent multicore DSPDigital audio processing is evolving into an art…Read More

Sophisticated soundscapes usher in cache-coherent multicore DSPDigital audio processing is evolving into an art…Read More A Quick Look at Agentic/Generative AI in Software EngineeringAgentic methods are hot right now since single…Read More

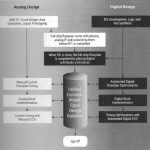

A Quick Look at Agentic/Generative AI in Software EngineeringAgentic methods are hot right now since single…Read MoreMixed-Signal Methodology Guide

Last week I reviewed Chapter 1 in the new book: Mixed-Signal Methodology Guide, and today I finish up my review of Chapters 2 through 11. You can read the entire book chapter by chapter, or just jump directly to the chapters most related to your design role or project needs. With multiple authors I was impressed with the wide range of… Read More

Mixed-Signal Methodology Guide

Last week I reviewed Chapter 1 in the new book: Mixed-Signal Methodology Guide, and today I finish up my review of Chapters 2 through 11. You can read the entire book chapter by chapter, or just jump directly to the chapters most related to your design role or project needs. With multiple authors I was impressed with the wide range of… Read More

TSMC 28nm Update Q3 2012!

Reports out of Taiwan (I’m in Hsinchu this week) have TSMC more than doubling 28nm wafer output in Q3 2012 due to yield improvements and capacity increases while only spending $3.6B of the $8.5B forecasted CAPEX! Current estimates have TSMC 28nm capacity at 100,000 300mm wafers (+/- 10%) per month versus 25,000 wafers reported… Read More

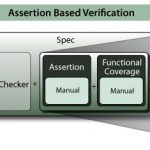

Assertion Synthesis

In June, Atrenta acquired NextOp, the leader in assertion synthesis. So what is it?

Depending on who you ask, verification is a huge fraction, 60-80%, of the cost of an SoC design, so obviously any technology that can reduce the cost of verification has a major impact on the overall cost and schedule of a design. At a high-level, verification… Read More

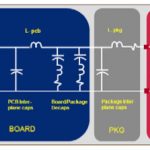

Power, Signal, Thermal and EMI signoff

Increasingly the challenge with SoCs, especially for mobile, is not getting the performance high enough but doing so in a power-efficient manner. Handheld devices running multiple apps need high-speed processors that consume extremely low levels of power both in operating and standby modes. In the server farm, the limit is … Read More

Apple’s Victory Will Re-Shuffle the Semi Industry

Apple’s legal victory over Samsung has been analyzed in thousands of articles and TWEETs since last Friday’s announcement and surely more will follow. Most of the commentary has focused on the first order impact to handset manufacturers. It is not entirely clear how it will all settle but there are sure to be secondary ramifications… Read More

A Brief History of FPGAs

From the transistor to the integrated circuit to the ASIC, next comes programmable logic devices on the road to the mainstream fabless semiconductor industry. PLDS started in the early 1970’s from the likes of Motorola, Texas Instruments, and IBM but it wasn’t until Xilinx brought us the field programmable gate array (FPGA)… Read More

SpringSoft Laker vs Tanner EDA L-Edit

Daniel Payne recently blogged some of the integration challenges facing Synopsys with their impending acquisition of SpringSoft. On my way back from San Diego last week I stopped by Tanner EDA to discuss an alternative tool flow for users who find themselves concerned about the Laker Custom Layout road map.

Design of the analog… Read More

IP Wanna Go Fast, Core Wanna Not Rollover

At a dinner table a couple years ago, someone quietly shared their biggest worry in EDA. Not 2GHz, or quad core. Not 20nm, or 450mm. Not power, or timing closure. Call it The Rollover. It’s turned out to be the right worry.

Best brains spent inordinate hours designing and verifying a big, hairy, heavy breathing processor core to do … Read More

Memory Innovation at the Edge: Power Efficiency Meets Green Manufacturing