The worldwide semiconductor market is back to a healthy level of growth. WSTS data shows the 2Q 2013 global semiconductor market was up 6.0% from 1Q 2013 – the strongest quarter-to-quarter growth since 6.6% growth in 2Q 2011. Recent forecasts for 2013 market growth range from a conservative 2.1% from WSTS to an optimistic… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

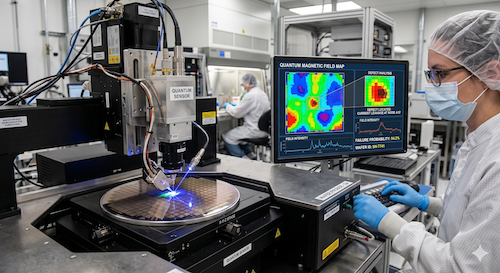

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read MoreFoundry 2.0: Why It Is Different And Why You Should Care

If you have been to an Ajit Manocha keynote recently, he talks a lot about Foundry 2.0. I covered his keynote at Semicon West in July here. Dan Hutcheson of VLSI Research interviewed Ajit about this new business model to identify it, see how it was different and see how GlobalFoundries were executing the model differently from the … Read More

Imagination Has More Stuff Than You…Imagine

Imagination seems to be well known for a couple of things. Firstly, everyone knows that it is the graphics processor used in the iPhone and the iPad and lots of other phones. And they know that Imagination acquired MIPS at the start of this year.

But what people don’t seem to really appreciate is just what a huge portfolio of IP… Read More

It’s a 14nm photomask, what could possibly go wrong?

Let’s start with the bottom line: in 14nm processes, errors which have typically been little more than noise with respect to photomask critical dimension (CD) control targets at larger process nodes are about to become very significant, even out of control if not accounted for.… Read More

FPGAs The Life Savers

Silicon dominates our lives, CPU’s, GPU’s are in the limelight but the unsung hero is the FPGA. They simply do the work where other silicon dare not tread, as they are unfit for the task. Never send a boy to do a man’s job.

For a moment, if we can, just for a few minutes perhaps we can break away from the social media bubble… Read More

Mobile SoC will benefit now from M-PCIe

We have already discussed the recently released M-PCIe ECN from PCI-SIG in Semiwiki at the end of 2012, but the new “standard” (in fact an Engineering Change from PCI-SIG and MIPI Alliance) was only real on paper, at that time. The upcoming webinar from Synopsys, M-PCIe: Utilizing Low-Power PCI Express in Mobile Designs, shows … Read More

Wall St. Takes the Wheel at Wintel

It now appears that Steve Ballmer was suddenly given his walking papers at the urging of an activist investor (ValueAct) and with the concurrence of Bill Gates. Wall Street’s growing impatience tends to coincide when the Innovators Dilemma scenario has taken hold of a company that has been unable to overcome its challengers. Why… Read More

Ballmer’s Retirement Leaves Nokia High and Dry

It looks to me as if Ballmer’s planned resignation from Microsoft is going to leave Nokia high and dry without an operating system. Because any successor to Ballmer will cancel Windows Phone which has managed to take Microsoft’s penetration in smartphones from 5% before it had a serious partnership with Nokia all … Read More

LSI’s Experience With Formality Ultra

LSI is an early adopter of Formality Ultra, Synopsys’s tool for improving the entire ECO flow. I already wrote about the basic capability of the tool here. ECOs are changes that come very late in the design cycle, after place and route has already been “nearly” completed. They occur either due to last minute spec… Read More

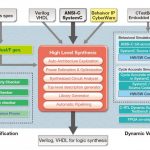

Something old, something new in SystemC HLS

Perhaps no area in EDA has been as enigmatic as high-level synthesis (HLS). At nearly every industry event, some new-fangled tool always seems to be tabbed as the next big thing by some analyst or pundit. In a twist, the latest news is on one of the oldest tools – CybeWorkBench.… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior