Recently I had a chance to chat with Arasan Ganesan, CEO at Arasan Chip Systems in San Jose, CA. Arasan Chip Systems has provided Silicon interface IP and supporting hardware and software to the semiconductor industry for more than 15 years. The headquarters are in San Jose and engineering offices in Bangalore and Tuticorin, India.… Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More

Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read More

Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read MoreTesting an IC Sandwich

At a lovely, but chilly, 3DIncites awards breakfast during SEMICON West, I saw Mentor Graphics win in two of five categories (Calibre 3DSTACK was the other winner). Afterwards, I talked to Steve Pateras, the product marketing director of Mentor’s test solutions about Tessent Memory BIST, which was one of the winners. I asked Pateras… Read More

Aldec Verifies Compatibility of Northwest Logic’s PCI Express Cores with HES-7™ SoC/ASIC Prototyping Platform

Henderson, Nevada – July 11, 2013 –Aldec, Inc., a pioneer in mixed HDL language simulation and hardware-assisted verification solutions, today announced that engineers incorporating high-speed PCI Express data transmission into their SoC and ASIC designs can accelerate their time-to-market utilizing Northwest Logic… Read More

Data Centers accounts for 2 to 3% of WW Energy Consumption!

Do you think this figure will go down? Considering the massive move to Mobile equipment, pushing to de-localize your storage medium to instead use the cloud capabilities, and looking at the huge number of people buying smartphone and tablet in emerging countries, no doubt that Data Center related energy consumption is expected… Read More

The Semiconductor IDM Business Model is Dead!

While this was not specifically stated, it was certainly implied during the sessions I attended at SEMICON West this week: The traditional semiconductor business model (IDM) is coming to an end. Starting with the keynote: Foundry-driven Innovation in the Mobility Era,cost was the common theme in any discussion involving mobile… Read More

Analysis of HLS Results Made Easier

In a recent article I discussed how easy it was to debug SystemC source code as shown in a video published on YouTube by Forte Design Systems. I also commented on the usefulness of the well-produced Forte video series. Today, I am reviewing another video in that series on analyzing high-level synthesis (HLS) results.

Cynthesizer… Read More

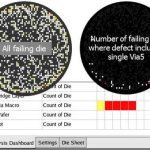

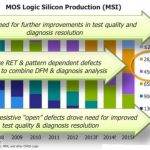

A Goldmine of Tester Data

Yesterday at SEMICON West I attended an interesting talk about how to use the masses of die test data to improve silicon yield. The speaker was Dr. Martin Keim, from Mentor Graphics.

First of all, he pointed out that with advanced process nodes (45nm, 32nm, and 28nm), and new technologies like FinFETs, we get design-sensitive defects.… Read More

Best Practices for Using DRC, LVS and Parasitic Extraction – on YouTube

EDA companies produce a wealth of content to help IC engineers get the best out of their tools through several means:

- Reference Manuals

- User Guides

- Tutorials

- Workshops

- Seminars

- Training Classes

- Phone Support

- AE visits

Towards the 0 DPM Test Goal

At Semicon yesterday I attended Mentor’s presentation on improving test standards. Joe Sawicki was meant to present but he was unable to get a flight due to the ongoing disruption at SFO after last weekend’s crash. I just flew in myself and it is odd to see the carcase of that 777 just beside the runway we landed on.

The … Read More

Apple iOS7 Will Drive The Next Semiconductor Cycle

We have entered the Summer lull, the quiet period before what is likely to be Apple’s largest volume launch of smartphones ever. While the launches are coming in like clockwork, it is the magnitude of the ramp that is likely to surprise many and it will be due not just to the features of iOS7, but also to the adoption of a well-worn Microsoft… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?