You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

I first heard about Andrew Yang back in 1993 when he founded a Fast SPICE company called Anagram, then acquired by Avant! in 1996. Andrew’s latest EDA company Apache Design, Inc.was started in 2001, then acquired by ANSYS in 2011. Most EDA mergers simply don’t work because of one or more reasons, like:

…

Read More

There are several events in Silicon Valley coming up of general interest to people working in EDA and the semiconductor industry.

SEMI 16th Annual Valley Lunch Forum. August 22nd, 11.30am to 1.30pm, Santa Clara Marriott

- What are the Opportunities for Advanced Semiconductor Devices?

- Where will the year end for 2013?

- Will we have

…

Read More

So Blackberry (formerly known as Research In Motion or RIM) is up for sale. Basically, apart from some cash in the bank, its main value now seems to be patents and, perhaps, some security technology. The murderers are in Cupertino and Mountain View, Apple’s iPhone (and iPad) and Google’s Android along with its licensees,… Read More

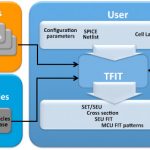

There are two ways to see how resistant your designs are to single-event errors (SEE). One is to take the chip or even the entire system and put it in a neutron beam and measure how many problems occur in this extreme environment. While that may be a necessary part of qualification in some very high reliability situations, it is also … Read More

Gary Smith has been talking about how the electronic system level (ESL) is where the future of EDA lies as design teams move up to higher levels encompassing IP blocks, high level synthesis, software development using virtual platforms and so on. At DAC this year in Austin he talked about how the fact that EDA controls the modeling… Read More

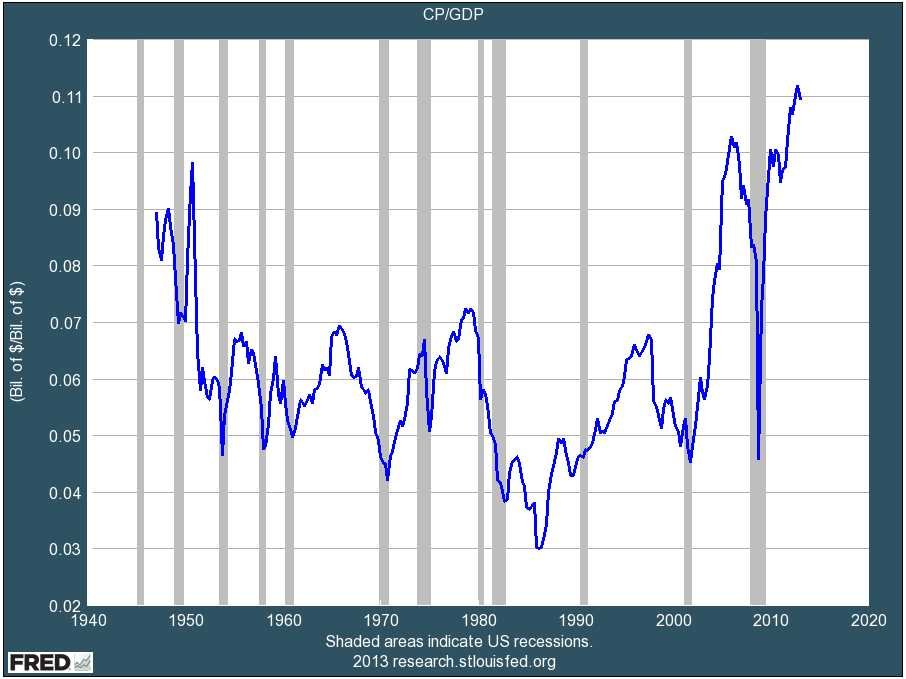

After driving to Silicon Valley for the past 30 years I am acutely aware of traffic patterns and to me that directly relates to the economy. The recession of 2009 really hit traffic patterns with what I would estimate as a 20% unemployment rate in Silicon Valley. I could leave my home in Danville anytime of the day and have no traffic … Read More

My Samsung Galaxy Note II lasts about two days on a single battery charge, which is quite the improvement from the Galaxy Note I with only a one day battery charge. Mobile SoCs are being constrained by battery life limitations, and consumers love longer-laster devices.

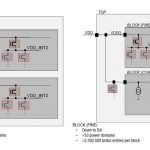

There are at least two approaches to Design For Power:

…

Read More

I could have written the sequence of the title in reverse order, but no, design is the one which initiates the need of a particular flow and the flow needs support of EDA tools to satisfy that need. It’s okay if the design is small; some manual procedures and workarounds/scripts may be able to perform certain jobs. However, as the design… Read More

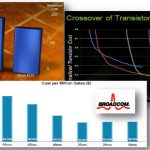

Back in May, William Holt, EVP of technology and manufacturing at Intel gave a presentation to analysts entitled Advancing Moore’s Law, Imperatives and Opportunity. A pdf of the presentation is available here. I just saw it for the first time today and I’m not sure how to get my head around it. It starts off with a lot … Read More

Your cell-phone contains a camera. In fact, it probably contains two: one forward facing for video-calls and one rear-facing for taking photographs and videos. The rear-facing one typically has much higher pixel count than the front-facing. The capabilities of cell-phone cameras are getting “good enough” that… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center