Actually these days even Baskin-Robbins has more, but not 505. But as it says in the title, Atmel have 505 different microcontrollers. That’s a lot. Some are AVR, both 8 bit and 32 bit, and some are various flavors of ARM (all 32 bit) ranging from older parts like the ARM9 to various flavors of Cortex ranging from the M0 (tiny microcontroller… Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

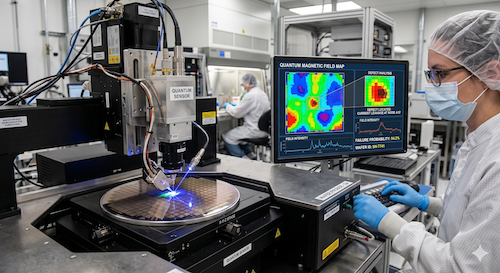

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More #DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read MoreXilinx vs. Altera DSP

Did you know in the Xilinx Virtex 28nm series you can REALLY run the DSP at 741 MHz? I say ‘really’ as you know dear reader, not all the FPGA claims of speed and usage tends to live up to reality. I cannot stand marketing games where you can run at a GHz ‘But’ and then comes the list of gotcha’s. Don’t believe me? Whaaat? Well let’s take a journey… Read More

Sir Hossein Yassaie, CEO of Imagination Technologies, Keynote!

Semiconductor IP is a focus of this year’s Design Automation conference and I’m excited to see a keynote by one of the leaders of this market segment. Even more interesting, Dr. Hossein Yassaie was knighted by the Queen in Her Majesty’s New Year Honours 2013. The award was given in recognition of his services to technology… Read More

Effect of Inductance on Interconnect

In previous design generations interconnect could safely be modeled by extraction using just R and C values. Parasitics in interconnect are important because they can affect the operating frequency or phase error in circuits like VCO’s. The need to model parasitics properly in wires is just as applicable in PA’s, LNA’s and for… Read More

Gobi, the Jewel in Qualcomm’s Crown

Back in the 1990s in the middle of the 2G GSM era, cell-phone manufacturers would display a “triangle of difficulty” with a large base labeled radio, a middle smaller part labeled baseband and a little triangle on top labelled software. The idea was that the radio was incredibly difficult, then the baseband chip and… Read More

GlobalFoundries Fab 8: Jobs

GlobalFoundries was created by spinning out the manufacturing side of AMD’s semiconductor business. Initially the company was jointly owned by AMD and by the Advanced Technology Investment Company (ATIC) which is an investment arm of the Emirate of Abu Dhabi. A couple of years ago ATIC bought out the remaining share from… Read More

Locked on FPGA design brand recognition

Back in the days where computing was dominated by a few big (and now mostly dearly departed) names, there was a saying: “Nobody ever got fired for buying IBM.” The relative safety of immediate brand recognition, especially among non-technical upper management, dissuaded many users from recommending or even seeking out other … Read More

Synopsys’s Next Generation Emulator, ZeBu Server-3

Since Synopsys acquired Eve over a year ago, they haven’t announced anything new in the ZeBu product line. Emulators are not like software where you expect incremental releases a couple of times per year, each new “release” is a complete re-design using new hardware fabric in a new process technology. Earlier… Read More

Friday Miscellany: EDAC Mixer, DVCon, DVCon Europe

Yesterday evening was EDAC’s first mixer. I assume the first of a regular event. It was held in Mountain View in the old train station which is now the Savvy Cellar wine bar. I had a nice glass of rosé from Provence that reminded me of the years that I lived in the south of France. Some of the money we spent went to charity, to the Mountain… Read More

Mixed-Signal SoC Debugging & IP Integration Made Easy

A semiconductor SoC design can have multiple components at different levels of abstractions from different sources and in different languages. While designing an SoC, IPs at different levels have to be integrated without losing the overall design goals. Of course, quality of an IP inside and outside of an SoC must be tested thoroughly.… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior