Last year at DAC I visited this little-known physical IP company called DXCorr, so I decided to visit them again this year and get an update.

Q: What type of Physical IP are you offering?

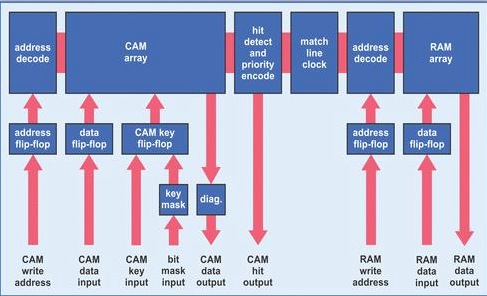

A: We have: CAMs, TCAMs (TSMC proven, 28nm and starting 16nm)

– Our goal is to have TSMC offer our libraries

Q: How would SoC customers use your IP?

A: With our Customers we enter a 3 way NDA with TSMC.

Q: What kind of customers do you have so far?

A: Our Markets are networking houses.

Last year – Japanese foundry, 40nm process, ram compilers.

LETI – European consortium that created FD SOI, will be meeting with them today. Technically interesting, unsure of the market demands.

Q: How was business in the past year?

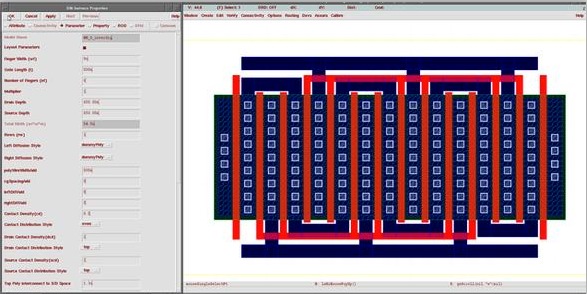

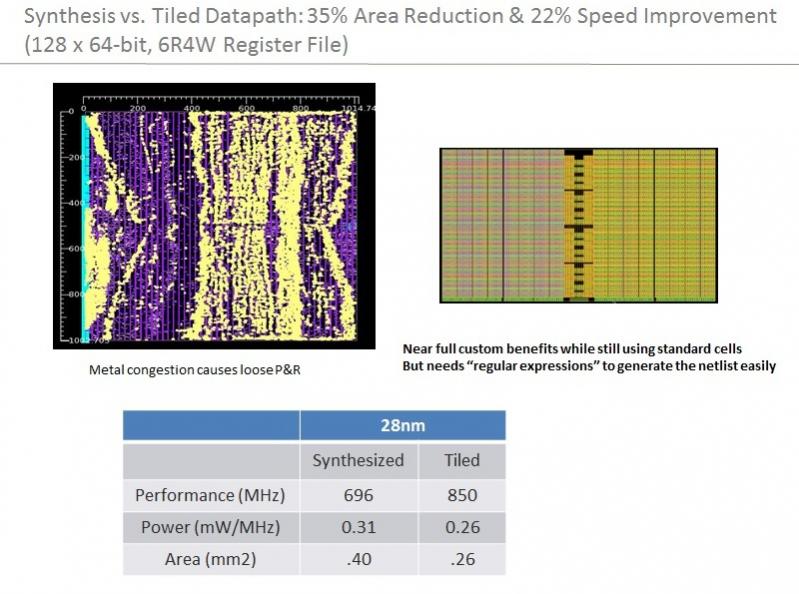

A: In 2013 the company has expanded, experts at generating regular layouts like Std Cell, Memory, CAM, Datapaths. How do I get the best performance with my placed instances? A consulting opportunity to make your IP work in a flow with Synopsys and Cadence.

Q: What kind of IP requests do you get?

A: Give me fast memories for my ARM processor. How do I get the best system specs? Best in practice scripts for EDA vendor tools. Meet power, timing, leakage budgets, and making trade-offs. HOw do you choose the right IP to meet your specs, where to place it in the layout.

ARM and Synopsys deliver IP instances, but not system optimizations.

Our compiler can create a memory subsystem with better specs than standard IP manually placed and optimized.

Q: When will we hear from the first DXCorr customer?

A: You will hear from ou first public customer this year.

Q: What types of consulting service do you offer?

A: Optimization with L2 cache and two cores, how to flooplan and reduce power by minimizing bus widths and placements, aspect ratios required. Help an architect reach their PPA goals. More like SoC planning, not true floorplanning.

Ask the IP user what their sub-system or SoC challenge is, then we can advise how to use it the best.

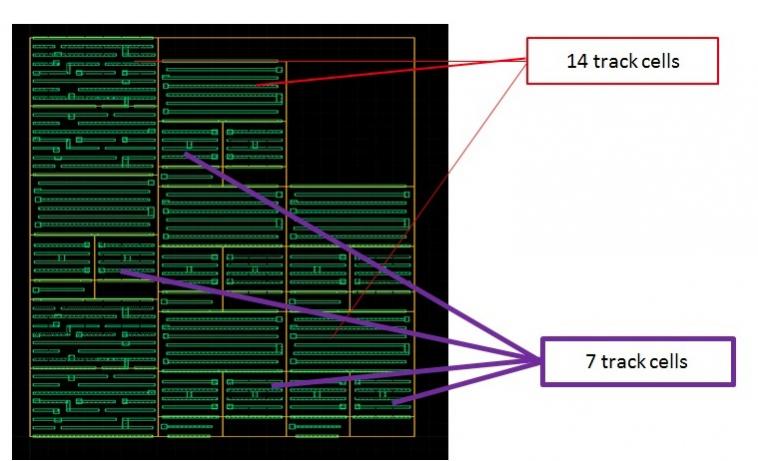

Example internal to a core, how to optimize a dozen blocks by minimizing interconnect and maintain timing. Create an optimal floorplan to drive your P&R tools. Flooplan to minimize power. Advise per IP block how many track libraries to use.

Last calendar year helped two customers on multiple projects.

PDK Services

Q: How is DXCorr different from other IP vendors?

A: We have IP + flow combination to make DXCorr different.

UP to 12 read 8 write ports at DXCorr.

Specialty IP can differentiate your SoC.

7/14 track std cell combination approach, different than others.

lang: en_US

Share this post via:

From the Selfie to Samantha: The Next Trillion-Dollar Behavior